# **BPEC Mission**

The mission of the Berkeley Power and Energy Center is to further research and education in the power and energy area through engagement with industry. We seek to create an ecosystem where leading academic researchers and top industry partners can share and exchange ideas in pre-competitive areas, advance the frontier of technology, and help educate the next generation of technology leaders in industry and academia.

Prof. Robert Pilawa-Podgurski, Director and Acting Executive Director

Prof. Jessica Boles, Co-Director, Power Electronics

Prof. Duncan Callaway, Principal Investigator, Power Systems

Prof. Emeritus Seth Sanders, Principal Investigator, Power Electronics

Dr. Sascha von Meier, Principal Investigator, Power Systems

Prof. Costas Spanos, Principal Investigator, Energy Efficiency

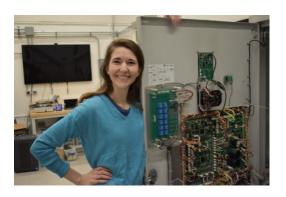

# **BPEC Students**

Dr. Samantha Coday

Margaret Blackwell

Rose Abramson

Nathan Brooks

Kelly Fernandez

Marrin Nerenberg

Logan Horowitz

Dr. Ting Ge

Rod Bayliss III

Yicheng Zhu

Rahul lyer

Joseph Schaadt

Sahana Krishnan

Jiarui Zou

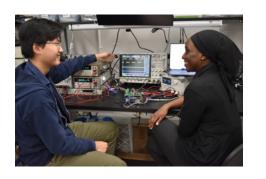

Haifah Sambo

Francesca Giardine

Ben Liao

Nathan Biesterfeld

Elisa Krause

Nagesh Patle

# **BPEC Students**

Sourav Naval

Wentao Xu

Dr. Mustapha Touhami

Tahmid Mahbub

# Research Programs

Power Components and Devices

Circuit Topologies and Control

Grid Integration – Systems and Technologies

# **Application Areas**

- Intellectual property rights to all inventions from BPEC sponsored research

- Early access to inventions and prepublications

- Attendance at annual research review meetings at UC Berkeley campus

- Representation on Industrial Advisory Board

- Access to electronically archived BPEC theses, papers, presentations, tutorials, and webinars

- Opportunity to direct funding to projects of particular interest to sponsor

- Opportunity to send Visiting Industrial Fellow to BPEC

- Access to students and faculty for research discussions and visits

- Resume book for all BPEC graduate and undergraduate students

- Opportunity to advertise career opportunities to power and energy courses

- Educational tutorials on topics of interest to industry

# Membership levels

- Regular Member: \$60,000 annually

- Collaborative Member (CM): \$160,000 annually

- Ability to directly support a Collaboration Membership Supported Project, in an area of interest to sponsor

- Additional CM projects: \$100,000 annually

- For more information and how to join, please visit bpec.berkeley.edu

#### **Berkeley Power and Energy Center**

Powering Tomorrow's Industry with Today's Research and Education

APPLICATIONS ~

**EVENTS**

TECHNOLOGIES ~

**CONTACT US**

EDUCATION ~

PEOPLE

MEMBERSHIP ~

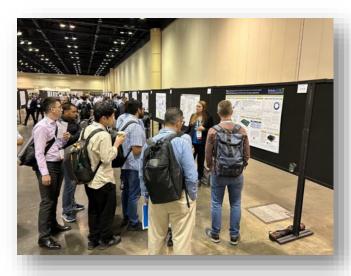

#### Come visit us at ECCE 2023!

BPEC will have an expo booth at ECCE from 4pm-7:30pm October 30 and 8:30am-11:30am and 5pm-7:30pm Wednesday, October 31.

Come talk to BPEC researchers and learn more about the center.

The mission of the Berkeley Power and Energy Center (BPEC) is to further research and education in the power and energy area through engagement with industry. We seek to create an ecosystem where leading academic researchers and top industry partners can share and exchange ideas in pre-competitive research areas, advance the frontier of technology, and help educate the next generation of technology leaders. Discover more about BPEC here.

Join BPEC

BECOME A MEMBER CONTACT US

# BPEC - Powering Tomorrow's Industry with Today's Research and Education

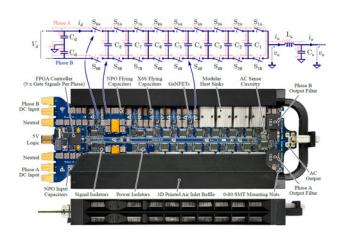

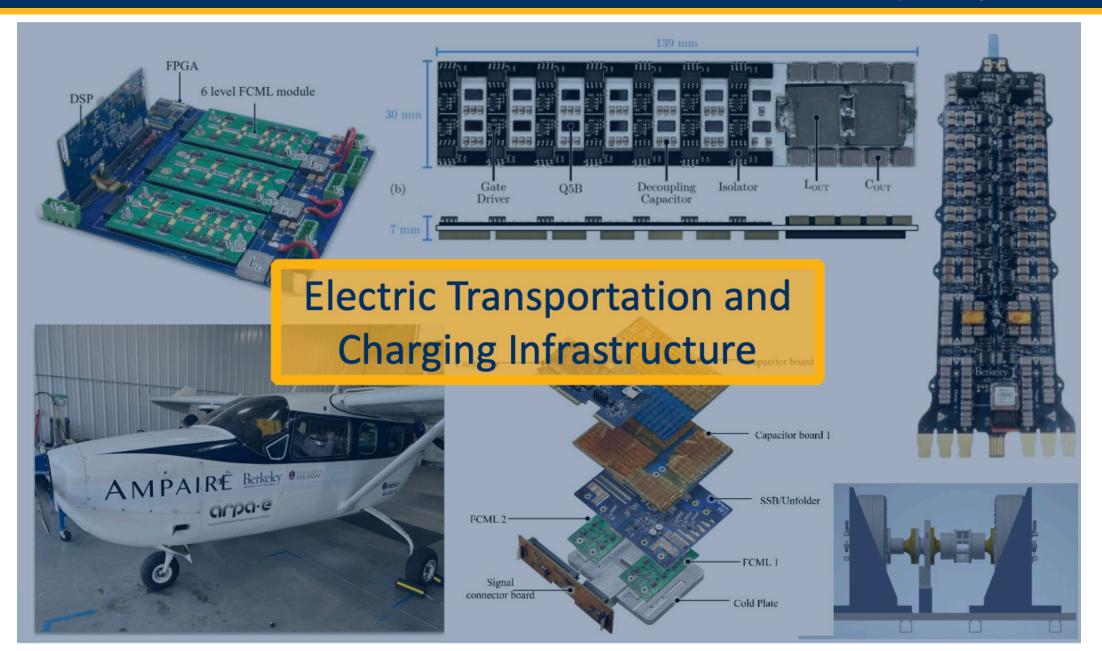

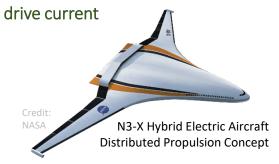

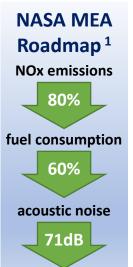

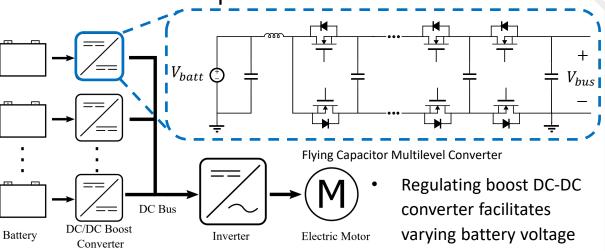

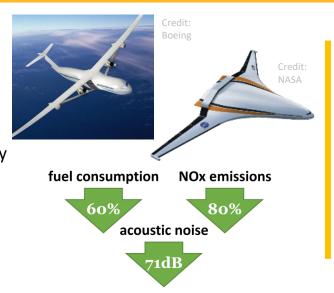

# Extreme Performance Scalable Inverter Architecture for More Electric Aircraft (MEA) Propulsion

# Motivation and Application

- Commercial aviation benefits from electric & hybrid vehicles

- Electric engines can be quieter and cleaner than jet engines

- Electric drive system must be power-dense and efficient

- Advanced power dense motors<sup>2</sup> need low THD, high frequency

University of Illinois

1 MW Motor Concept <sup>2</sup>

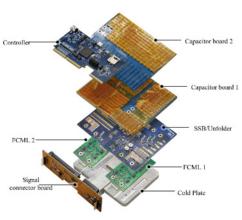

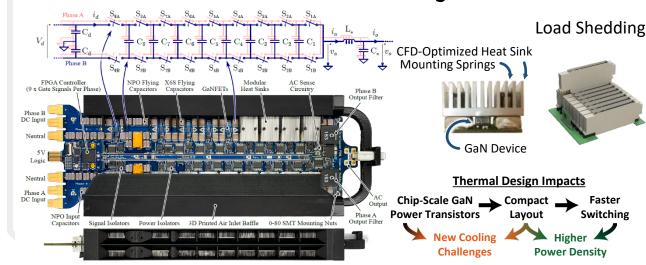

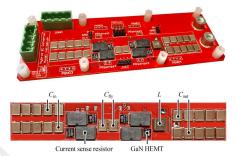

# Electrical, Mechanical and Thermal Management Hardware

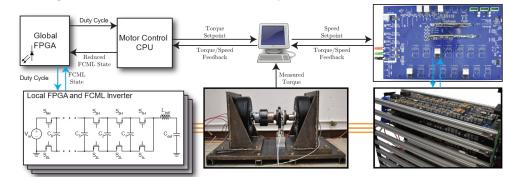

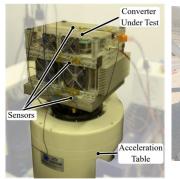

# High Power Dynamometer

- Dyno incorporates two low-inductance Emrax 348 machines (peak power: 260 kW)

- Testing validated the Flying Capacitor Multilevel Converter's (FCML) strength in a realistic motor drive system

# **Experimental Verification or Other**

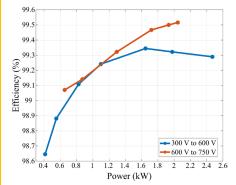

- Prototype meets NASA performance metrics for turbo-electric aircraft <sup>4</sup>

- Integration of advanced thermal management will boost maximum output power and efficiency

- Modular design provides for power scalability and fault resiliency

- Next steps: verification of floating-point motor control algorithm and high-power dyno and next generation inverter hardware development

|                 | NASA Target | This Work  |

|-----------------|-------------|------------|

| Peak Efficiency | 99%         | 98.95%     |

| Power Density   | 19 kW/kg    | 38.4 kW/kg |

References:

I. Pallo, R. S. Bayliss and R. C. N. Pilawa-Podgurski, "A Multi-Phase Segmented Drive Comprising Arrayed Flying Capacitor Multi-Level Modules," IEEE APEC 2021

- 1] N. Madavan, et al., "A NASA Perspective on Electric Propulsion Technologies for Commercial Aviation," 2016.

- [2] X. Zhang and K. Haran, "High-Specific-Power Electric Machines for Electrified Transportation Applications Technology Options," IEEE ECCE 2016

- [3] N. Pallo, et al., "Power-Dense Multilevel Inverter Module using Interleaved GaN-Based Phases for Electric Aircraft Propulsion," IEEE APEC 2

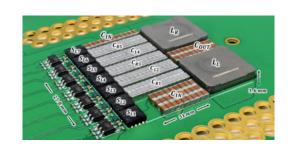

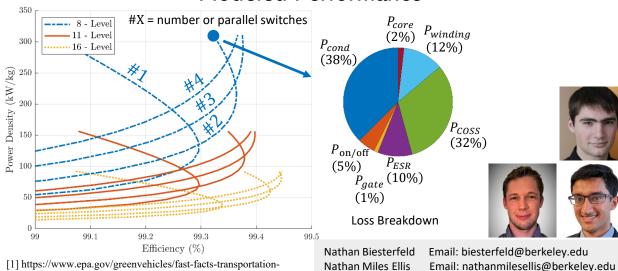

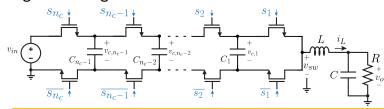

# Design of an Efficient, Lightweight Flying Capacitor Multilevel Converter for Electrified Flight

# Motivation and Application

- Air travel accounts for ~200 million tons of CO<sub>2</sub> emissions annually (3% of US greenhouse gas emissions)[1]

- Air travel demand is expected to double every fifteen years

- Electrification of flight requires efficient, lightweight, and reliable power conversion

- Hardware must be flight qualified

Pictured: Ampaire Electric EEL flight

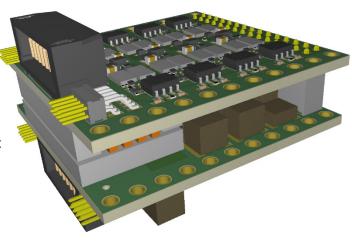

# Hardware Prototype

- Snubbers enable decreased overlap loss without sacrificing conduction path

- Paralleled switches enable increased areal power density

- Derated energy density metric used to optimize flying capacitor part/count

- Custom inductor achieves 3x mass reduction

greenhouse-gas-emissions

3D rendering of 8-level boost FCML prototype

Email: rkiyer@berkeley.edu

# **Proposed Solution**

#### Electric Aircraft Drivetrain Architecture

and inverter load demand

#### Modeled Performance

Rahul Iver

# Empowering Future Electric Aircraft with a Flying Capacitor Multilevel Inverter Utilizing Optimal Passive Components

# Motivation and Application

- Air travel accounts for ~200 million tons of CO<sub>2</sub> emissions annually (3% of US greenhouse gas emissions)<sup>[1]</sup>

- Air travel demand doubles every fifteen years

- Electrification of flight requires efficient, lightweight, and reliable power conversion

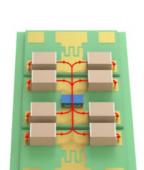

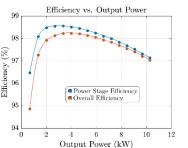

## Hardware Prototype

- 10 kW, 800 V, 14-level FCML

- Sandwich-style layout with two printed circuit boards

- Ultra-thin design, only 8 mm thick!

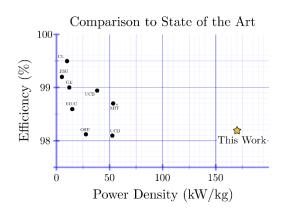

| <b>Key Converter Parameters</b>  |                         |  |

|----------------------------------|-------------------------|--|

| Input Voltage                    | 800 V <sub>DC</sub>     |  |

| Output Voltage                   | 270<br>V <sub>RMS</sub> |  |

| Effective Switching<br>Frequency | 1.95<br>MHz             |  |

| Peak Output Power                | 10.3 kW                 |  |

| Peak Overall Efficiency          | 98.2 %                  |  |

| Gravimetric Density              | 170<br>kW/kg            |  |

| Volumetric Density               | 370<br>kW/L             |  |

|                                  |                         |  |

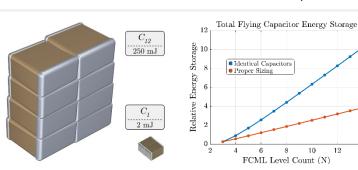

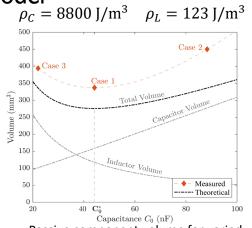

# FCML with Optimal Passive Component Selection

Simplified 14level FCML schematic

#### **Capacitor Sizing**

- Conventional approach utilizes large, identical capacitors

- Proposed approach optimally selects unique capacitors for each flying capacitance

- Enables > 50% reduction in size

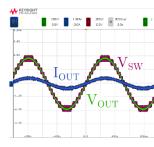

# **Experimental Verification**

- Highest power density among state-of-the-art aircraft inverters

- Excellent capacitor balancing and low output distortion despite the small size of the converter

#### References:

$\hbox{[1] https://www.epa.gov/greenvehicles/fast-facts-transportation-greenhouse-gas-emissions}\\$

Logan Horowitz | Email: logan h horowitz@berkeley.edu

# Tethered Power Systems for Lunar Mobility and Power Transmission (TYMPO)

Berkeley Power and Energy Center

# Motivation and Application

Extreme terrain capable robots will enable further exploration on sites such as pits on the moon and Martian landscape. Tethered power systems have been proposed to power these small rovers; however, they require high voltage DC power [1].

#### Challenges

High voltage switches are difficult to use in space due to radiation effects. Additionally, the high voltage conversion ratio makes it difficult to design a compact and efficient power converter.

Therefore, multilevel topologies offer promising solutions [2].

Tethered rover to explore lunar pits

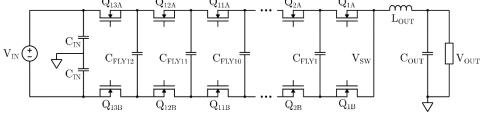

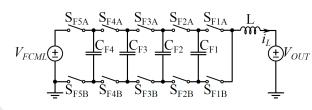

# System Architecture (Flying Capacitor Multilevel Converter)

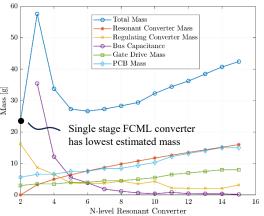

- Comparison of cascaded structure consisting of resonant flying capacitor multilevel converter (FCML) and regulating FCML (resonant FCML + regulating FCML) vs single-stage FCML converter

- Bus capacitance requirement diminishes benefits of cascaded structure

FCML converter schematic

Estimated mass breakdown of cascaded FCML converter structure

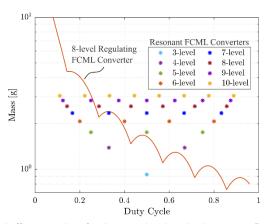

### Passive Mass Minimization

- Comparison of 8-level regulating mode FCML converter with a resonant mode FCML converter, demonstrating the advantages of a resonant converter in terms of passive component mass

- Each converter operating point is optimized for minimal mass based on the peak energy storage requirements of the passive components

#### References:

- [1] P. McGarey, W. Reid and I. Nesnas, "Towards Articulated Mobility and Efficient Docking for the DuAxel Tethered Robot System," 2019 IEEE Aerospace Conference, 2019, pp. 1-9.

- [2] P. McGarey, T. Nguyen, T. Pailevanian and I. Nensas, "Design and Test of an Electromechanical Rover Tether for the Exploration of Vertical Lunar Pits," 2020 IEEE Aerospace Conference, 2020, pp. 1-10.

- [3] S. Coday, A. Barchowsky and R. C. N. Pilawa-Podgurski, "A 10-level GaN-based Flying Capacitor Multilevel Boost Converter for Radiation-Hardened Operation in Space Applications," 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), 2021, pp. 2798-2803.

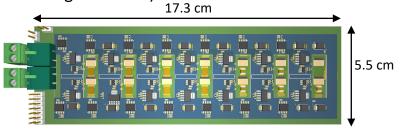

### Hardware Verification

840 V-to-120 V space-rated FCML converter to verify:

- PCB structure (Gate drive daughterboard)

- Part selection

- Thermal solutions

- Mass optimization

Student: Elisa Krause, Maggie Blackwell, Logan Horowitz Email: {elisa\_Krause, blackwell, logan\_h\_horowitz}@berkeley.edu

# On the Size and Weight of Passive Components: Scaling Trends for High-Density Power Converter Designs

Berkeley Power and Energy Center

# Motivation and Application

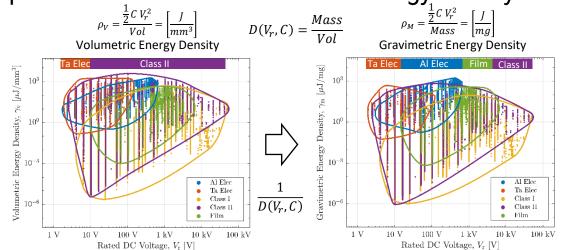

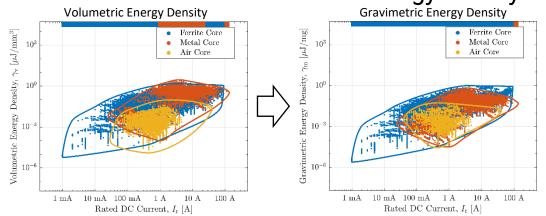

To build a high-density power converter, practicing engineers need to use passive components with the highest density.

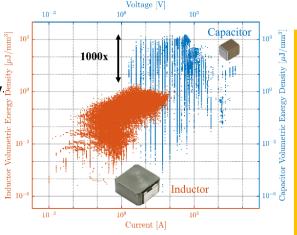

- A component survey finds Volumetric Energy Density.

- Visualized to assist component selection.

- But how to estimate Gravimetric Energy Density?

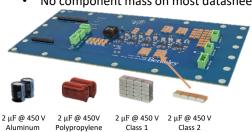

- · No component mass on most datasheet.

Volumetric Energy Density determined by a component survey encompassing over 606,000 capacitors and 88,000 inductors

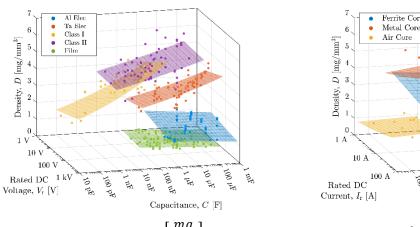

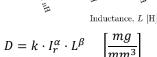

## Power Fit Estimation for Specific Density (D)

$$D = k \cdot V_r^{\alpha} \cdot C^{\beta} \qquad \left[ \frac{mg}{mm} \right]$$

Mass data was obtained through manual measurements of over 6,000 components

# Capacitor Volumetric vs. Gravimetric Energy Density

Inductor Volumetric vs. Gravimetric Energy Density

Volumetric Energy Density

Gravimetric Energy Density

References: J. Zou, N. C. Brooks, S. Coday, N. M. Ellis and R. C. N. Pilawa-Podgurski, "On the Size and Weight of Passive Components: Scaling Trends for High-Density Power Converter Designs," 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL), Tel Aviv, Israel, 2022, pp. 1-7, doi: 10.1109/COMPEL53829.2022.9829957.

Jiarui Zou, jiarui.zou@berkeley.edu; Nathan Brooks, nathanbrooks@berkeley.edu;

Samantha Coday, Scoday@berkeley.edu; Nathan Ellis, Nathanmilesellis@berkeley.edu

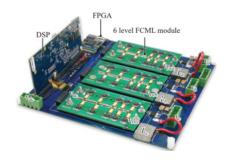

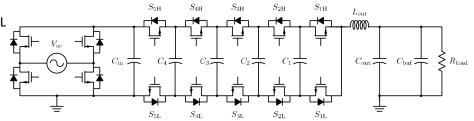

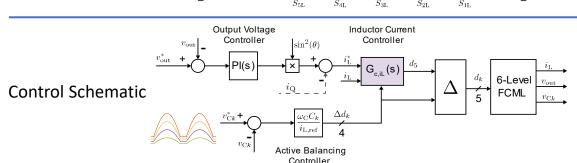

# Enabling Buck-Type AC/DC Grid-Tied Rectifiers Using Flying Capacitor Multi-Level Converters with Advanced Control

# Motivation and Application

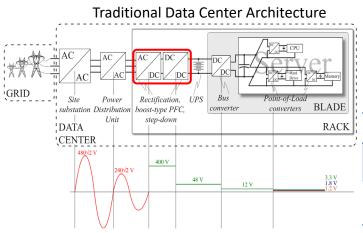

Data center power consumption 1%+ of global electricity demand and growing [1]

#### Single-stage rectification

- Increased efficiency

- Greater power density

#### Hardware

TI C2000 DSP (F28379D)

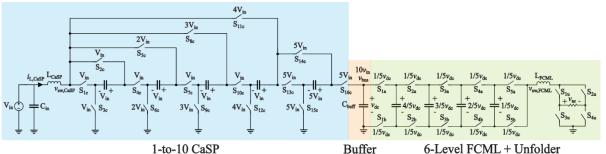

# FCML and Active Flying Capacitor Voltage Balancing

6-Level Buck-Type FCML

PFC Rectifier

• Reduced magnetics

volume

• High FOM switches

# **Experimental Verification**

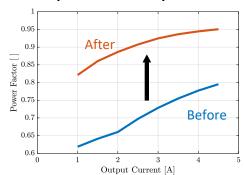

#### Power Factor

Target 0.97

Passive Balancing 0.88

**Active Balancing**

Switch voltage stress limited → low voltage switches

References:

0.97+

[1] N. Jones, "The Information Factories," Nature 2018

Rod Bayliss III Email: rodbay@berkeley.edu

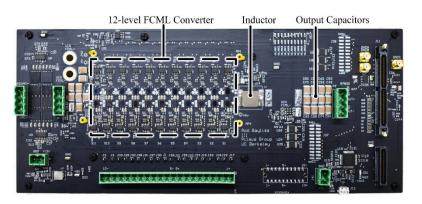

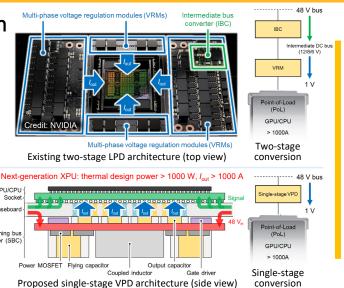

# A 1200-A/48-V-to-1-V Switching Bus Converter: Toward Single-Stage Vertical Power Delivery for Next-Generation Ultra-High-Power Microprocessors

Berkeley Power and Energy Center

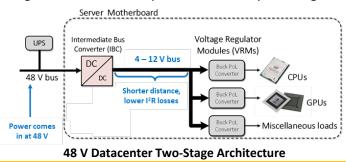

## Background and Motivation

**Existing** two-stage lateral power delivery (LPD) architecture

- Large power distribution network (PDN) and high PDN losses

- Occupies a large area on the top side of the baseboard

**Proposed** single-stage vertical power delivery (VPD) architecture

- Much lower PDN losses

- Saves the topside area for high-speed communication and memories

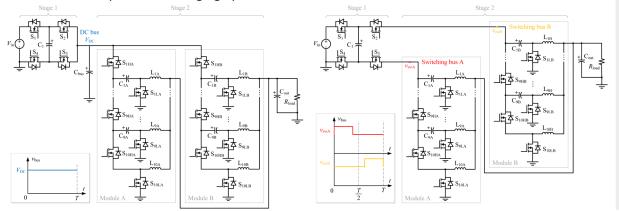

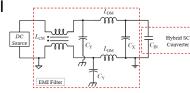

## Proposed Switching Bus Converter (SBC)

#### Hybrid switched-capacitor topology

- Two 2-to-1 switched-capacitor (SC) front-ends

- Four series-capacitor buck (SCB) modules

- Two switching buses

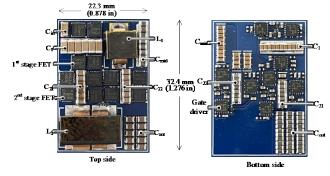

#### Hardware prototype

- Good modularity

- Custom four-phase coupled inductor

- Efficient and compact gate drive circuitry

Photograph of the hardware prototype

# Advantages of Switching-Bus-Based Architecture

- Does not require a large decoupling capacitor to maintain a stiff DC bus voltage

- · One redundant switch can be removed on each switching bus while two stages are merged

- · Ensures complete soft-charging operation

DC-bus-based architecture

Switching-bus-based architecture

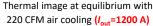

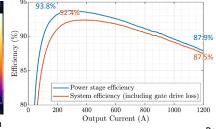

# Experimental Results and Performance Comparison

• 92.4% peak system efficiency and 607 W/in<sup>3</sup> power density (including gate drive loss and volume)

Measured 48-V-to-1-V efficiency

Performance comparison between this work and the state-of-the-art 48-V-to-1-V hybrid SC works

#### References:

- [1] Y. Zhu, et al., "A 48-V-to-1-V Switching Bus Converter for Ultra-High-Current Applications," COMPEL 2023. [Best Paper Award]

- [2] Y. Zhu, et al., "A 500-A/48-to-1-V Switching Bus Converter: A Hybrid Switched-Capacitor Voltage Regulator with 94.7% Peak Efficiency and 464-W/in3 Power Density," APEC 2023.

- [3] Y. Zhu, et al., "A Dickson-Squared Hybrid Switched-Capacitor Converter for Direct 48 V to Point-of-Load Conversion," APEC 2022.

Yicheng Zhu, Ting Ge, Nathan M. Ellis, and Jiarui Zou Email: {yczhu, gting, nathanmilesellis, jiarui.zou}@berkeley.edu

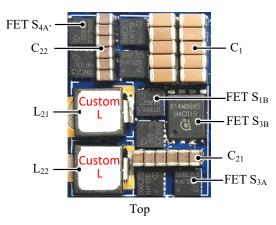

# 48-to-6 V Cascaded Series-Parallel Converter for **Intermediate Bus Applications**

# Berkeley Power and **Energy Center**

# Motivation and Application

Data center power delivery has recently moved to a 48 V bus, which must be stepped down at the server racks. Commonly, this bus is stepped down to a 12 V intermediate bus, which is then converted to the low voltage, high current rails needed at the point-of-load (PoL). However, lower (i.e. 4-8 V) intermediate bus voltages have shown promise in increasing overall system efficiency by allowing the 2<sup>nd</sup> stage PoL converter to operate at lower input voltages, and therefore higher efficiency.

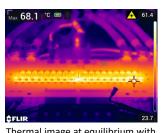

# **Experimental Validation**

The hardware prototype was designed using 25 V and 40 V Si MOSFETs (Infineon OptiMOS) and Class II ceramic capacitors. The inductor is recessed into the PCB to obtain a more power dense design.

#### **Operating Parameters**

|                  | Nominal | Range                 |

|------------------|---------|-----------------------|

| V <sub>in</sub>  | 48 V    | 40 – 60 V             |

| $V_{out}$        | 6 V     | $5-7.5\;V$            |

| $I_{out,max}$    | 70 A    | 70 A                  |

| P <sub>out</sub> | 400 W   | $330-500\;\mathrm{W}$ |

| $f_{sw}$         | 50 kHz  | 50 – 55 kHz           |

Thermal Photo at  $I_{out} = 70 \text{ A}$ Bottom side

The converter was able to maintain a temperature below 60°C at the full load current of 70 A with only fan cooling.

Dimensions: 1.76 x 0.51 x 0.21 in (44.7 x 13.0 x 5.3 mm)

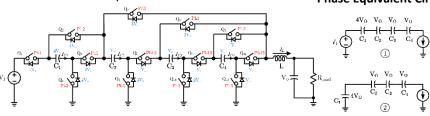

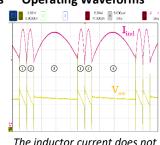

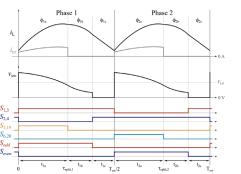

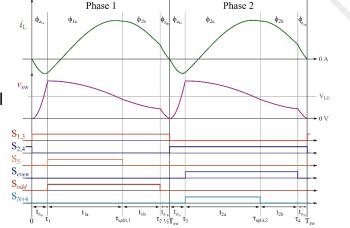

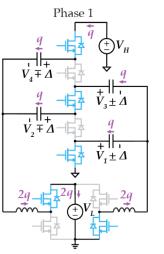

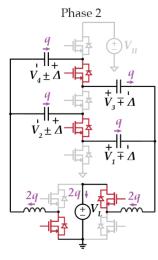

# Theory of Operation

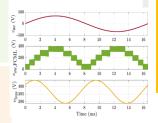

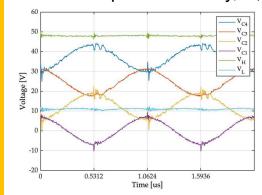

The 8:1 cascaded series-parallel (CaSP) converter consists of a 2:1 input stage merged with a 4:1 series-parallel converter. The multi-operating-phase operation allows the converter to achieve a high conversion ratio with fewer components compared to conventional two-phase hybrid switched capacitor circuits. The converter is operated above resonance to reduce RMS currents and make it less sensitive to capacitor tolerance variations. **Operating Waveforms**

Schematic of 8:1 CaSP Converter

#### [1] R. A. Abramson, Z. Ye, T. Ge and R. C. N. Pilawa-Podgurski, "A High Performance 48-to-6 V Multi-Resonant Cascaded Series-Parallel (CaSP) Switched-Capaciton Converter," 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 2021.

#### **Phase Equivalent Circuits**

The inductor current does not ripple all the way down to 0 A, owing to the above resonance operation.

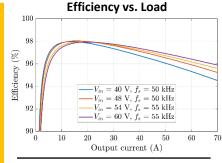

## Converter Performance

| $V_{in}$ | Peak Eff.<br>(%) | Full Load<br>Eff. (%) |

|----------|------------------|-----------------------|

| 40 V     | 98.0%            | 94.6%                 |

| 48 V     | 98.1%            | 95.3%                 |

| 54 V     | 98.0%            | 95.7%                 |

| 60 V     | 97.9%            | 96.0%                 |

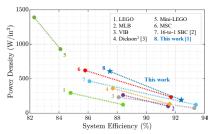

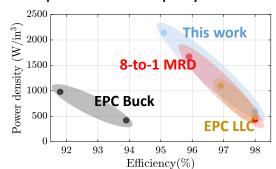

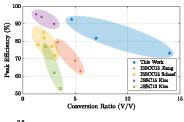

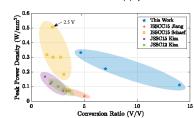

#### Comparison with Contemporary State of the Art

Each converter efficiency and power density is plotted at two points:

- 1) Peak efficiency load

2) Full load

Owing to the high overall efficiency, the converter exhibits an output droop of 292 mV (or 4.9% of V<sub>out</sub>), corresponding to an output impedance of 4.2 m $\Omega$ .

Rose Abramson Email: rose\_abramson@berkeley.edu

# A Bidirectional Liquid-Cooled GaN-based AC/DC Flying Capacitor Multi-Level (FCML) Converter with Integrated Startup and Additively Manufactured Cold-Plate for Electric Vehicle Charging

# Berkeley Power and Energy Center

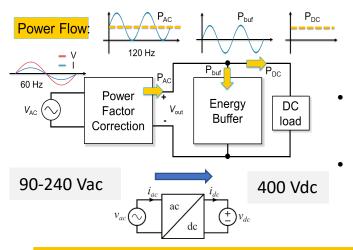

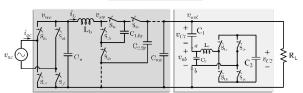

# Motivation and Application

- 90-240 Vac to 400 Vdc is a critical conversion stage for applications such as data center power delivery, electric vehicle charging, etc.

- Ac-dc power factor correction

Reduce boost inductor size

Twice-line frequency power ripple buffering

Reduce buffer capacitor size

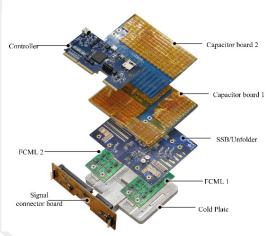

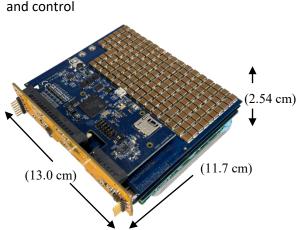

### Hardware Implementation

Modular stack-up of full system

# Decoupling Flying Capacitors Gate Driver Gan Transistors 49 mm

# Flying capacitor multi-level"(FCML) converter as the power factor correction stage

Use of flying capacitors as energy storage greatly decreases volume of passive components and reduce filtering needs

#### Series-stacked Buffer as energy buffer stage

Use of active circuitry decreases capacitance requirement for twice-line frequency buffering and further promoted volume reduction

## **Design Objectives**

#### **High Power Density**

Reduce system volume via new circuit topologies and control

#### Reduced Weight

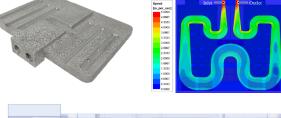

Custom 3D-printed cold-plate (collaboration with Miljkovic Group at UIUC)

3D printed cold-plate Printed Fluid Channels

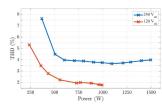

# Experimental Verification

| Parameter                                 | Notes    |

|-------------------------------------------|----------|

| Peak tested power                         | 6.1 kW   |

| Peak efficiency (1.1 kW)                  | 99.1%    |

| Efficiency @ 6.1 kW                       | 97.8%    |

| PFC up to 1.5 kW                          | > 99.6%  |

| Box-volume power density with cold plate: | 7.6 kW/L |

THD up to 1.5 kW

#### Kelly Fernandez, Rahul Iyer, Jiarui Zou

Email: kefernandez@berkeley.edu, rkiyer@berkeley.edu, Jiarui.zou@berkeley.edu

#### References:

- [1] D. Chou et al., "An Interleaved 6-Level GaN Bidirectional Converter with an Active Energy Buffer for Level II Electric Vehicle Charging," 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 2021

- [2] Z. Liao, D. Chou, K. Fernandez, Y.-L. Syu and R. C. N. Pilawa-Podgurski, "Architecture and Control of An Interleaved 6-Level Bidirectional Converter With an Active Energy Buffer for Level-II Electric Vehicle Charging," 2020 IEEE Energy Conversion Congress and Exposition (ECCE),

- [3] K. Fernandez et al., "A Bidirectional Liquid-Cooled GaN-based AC/DC Flying Capacitor Multi-Level Converter with Integrated Startup and Additively Manufactured Cold-Plate for Electric Vehicle Charging," 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 2022

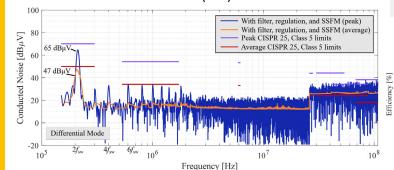

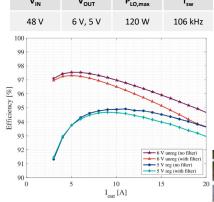

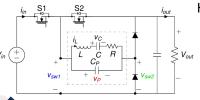

# An EMI-Compliant and Automotive-Rated 48 V-to-PoL Dickson-Based Hybrid Switched Capacitor DC-DC Converter

# Berkeley Power and **Energy Center**

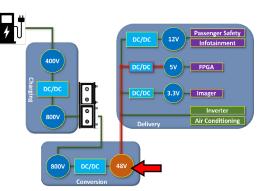

# Motivation and Application

Data center power delivery and automotive powertrains tending towards a 48 V distribution rail

• Higher intermediate bus voltages minimize losses and reduce cabling weight

This work demonstrates the merit of hybrid SC topologies for use in 48 V automotive systems

- Regulating Dickson-based hybrid SC topology

- EMI mitigation techniques filtering and spreadspectrum frequency modulation

48 V automotive bus architecture

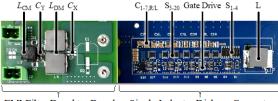

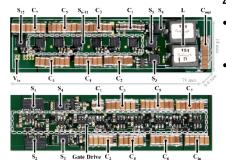

## Hardware Implementation

Uses only automotive-qualified parts

Switch selection based on required function, both Si and GaN

EMI input filter and spread spectrum frequency modulation (SSFM) to reduce EMI

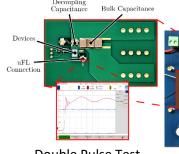

Input EMI filter schematic

| Switches and Key Parameters |                             |                      |                   |  |

|-----------------------------|-----------------------------|----------------------|-------------------|--|

| Switch                      | Switch S1-S4 S5-S18 S19-S20 |                      |                   |  |

| Tech                        | Si                          | Si                   | GaN               |  |

| Function                    | Bridge<br>switches          | 'String'<br>switches | Input<br>switches |  |

| R <sub>DS(on)</sub>         | 1.4 mΩ                      | $3.5\text{m}\Omega$  | 2.5 mΩ            |  |

| $V_{DS}$                    | 40 V                        | 40 V                 | 80 V              |  |

EMI Filter Daughter Board Single-Inductor Dickson Converter

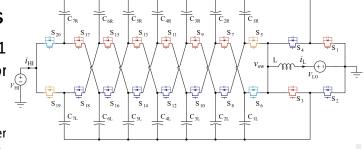

# Topology and Challenges

Hybrid switched-capacitor, 8-to-1 interleaved-input, single-inductor Dickson converter

- Differential input → continuous input current → reduced required input filter

- Inductor at output → filtering and EMI shielding at low side

- Inductor at output → voltage regulation

### Challenges

- Split-phase switching necessary for softcharging of the flying capacitors

- Automotive component selection

- High efficiency, power density, and CISPR 25 Class 5 EMI compliance

# **Experimental Results**

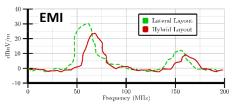

Differential Mode (DM) EMI results

Peak and average DM emissions plots for above-resonant (~106 kHz) regulated 5 V operation with SSFM enabled

References: [1] M. E. Blackwell, et al., "Direct 48 V to 6 V Automotive Hybrid Switched-Capacitor Converter with Reduced Conducted EMI," 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL). [2] S. Krishnan, et al., "An EMI-Compliant and Automotive-Rated 48V to Point-of-Load Dickson-Based Hybrid Switched-Capacitor DC-DC Converter," 2023 IEEE Transportation Electrification Conference & Expo (ITEC)

Measured efficiency of hardware prototype

Sahana Krishnan

Email: sahana krishnan@berkeley.edu Maggie Blackwell Email: blackwell@Berkeley.edu

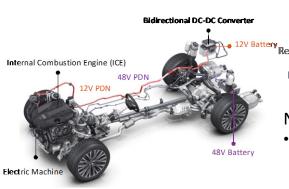

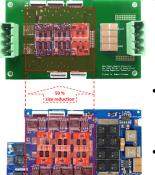

# Bidirectional Power Transfer in Hybrid Switched-Capacitor Converter for 48V/12V Regulated Automotive Applications

# Motivation and Application

Dual Battery System in Mild Hybrid Electric Vehicle (MHEV) (Source: Audi A8 Powertrain)

# AC Compressor Lighting Regenerative Braking Lighting Value 12V Ignition Integrated Starter Generator (ISG) Infotainment Lighting Infotainment Engine Management

#### Need:

48V battery should be able to deliver extra power to 12V battery based on increased load demand and vice-versa.

#### Challenges:

Delivery of high current with high efficiency and high power density in both directions

# Advantages of Proposed Control Technique

- Implements Natural Balancing of all flying capacitors.

- Achieves Soft-charging and soft-switching .

- Minimizes the size of the intermediate capacitor  $C_{mid}$ .

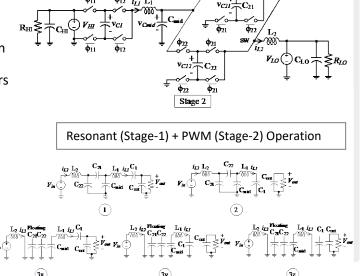

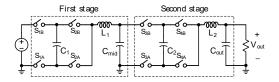

# Converter Topology

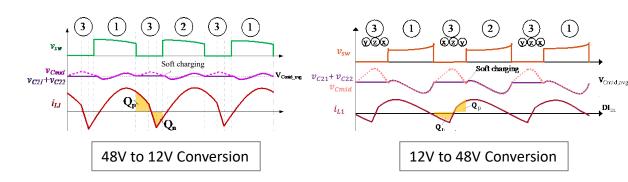

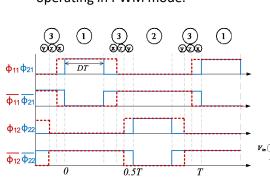

- 48V-to-12V regulated cascaded hybrid resonant-PWM converter [1]

- 1<sup>st</sup> stage uses a conventional doubler in resonant mode

- 2<sup>nd</sup> stage used two interleaved doublers operating in PWM mode.

## Hardware Demonstration and Results

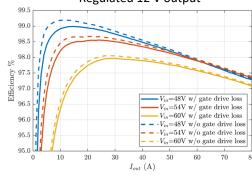

#### Measured Efficiency at:

- Input voltage: 48 60V

- 80 A full-load current

- Regulated 12 V output

[1] T. Ge, et. al., "A Regulated Cascaded Hybrid Switched-Capacitor Converter with Soft-Charging and Zero Voltage Switching for 48-to-12-V," 2023 IEEE APEC.

- 80A, 99% peak eff. 3115 W/in<sup>3</sup> power density

- 21% loss and 63% size reduction over SOTA

Nagesh Patle, Ting Ge Email: {nageshpatle,gting}@berkeley.edu

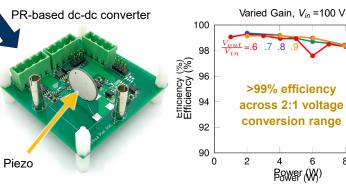

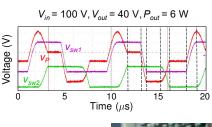

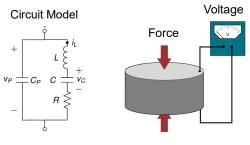

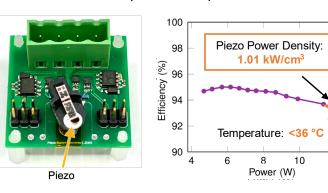

# Converter Topologies and Control Strategies Leveraging Piezoelectrics for High-Performance Miniaturized Power Conversion

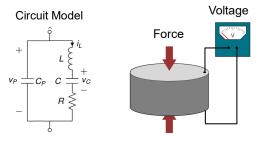

# Piezoelectrics as Passive Components

Magnetics present fundamental size and performance challenges at small scales

Piezoelectrics are promising alternative passives for miniaturized power conversion

Piezoelectrics store energy in mechanical compliance and inertia

- ✓ High power density

- ✓ High efficiency

- ✓ Isolation

- ✓ Planar form factor

- ✓ Batch fabrication

- ✓ Integration potential

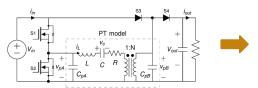

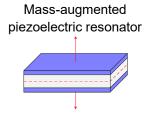

# Converter Topologies Based on Piezoelectrics

We develop converter topologies that leverage the advantages of piezoelectrics in a variety of applications

Piezoelectric-resonatorbased dc-dc converter

Piezoelectric-transformer-based dc-dc converter

Hybrid piezo / switched capacitor converter

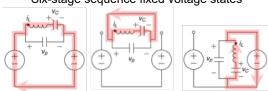

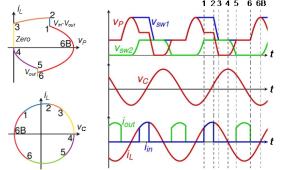

### Control for Efficient Utilization of Piezoelectrics

We develop high-performance switching sequences and control strategies tailored to optimal utilization of piezoelectrics

Pulse Width

Modulation

Dead Time

Six-stage sequence fixed voltage states

High-Efficiency Behaviors:

- Soft charging of Cp

- Soft switching of all switches

- Minimal charge circulation

#### Practical Characteristics:

- Wide voltage gain range

- Simple switch implementation

Six-stage sequence state trajectories and waveforms

# **Experimental Demonstration**

We experimentally demonstrate the high performance capabilities of piezoelectric-based power conversion

- J. D. Boles et al., "Enumeration and analysis of dc-dc converter implementations based on piezoelectric resonators," IEEE TPEL, 2021.

- J. D. Boles et al., "A piezoelectric-resonator-based dc-dc converter demonstrating 1 kW/cm³ resonator power density," IEEE TPEL, 2023.

- J. D. Boles et al., "Piezoelectric-based power conversion: recent progress, opportunities, and challenges,," IEEE CICC, 2022.

Prof. Jessica Boles boles@berkeley.edu

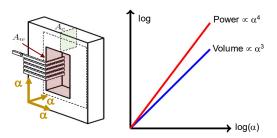

# Piezoelectric Passive Components for High-Performance Miniaturized Power Conversion

## Piezoelectrics as Passive Components

Magnetics present fundamental size and performance challenges at small scales

Piezoelectrics are promising alternative passives for miniaturized power conversion

Piezoelectrics store energy in mechanical compliance and inertia

- ✓ High power density

- ✓ High efficiency

- ✓ Isolation

- ✓ Planar form factor

- ✓ Batch fabrication

- ✓ Integration potential

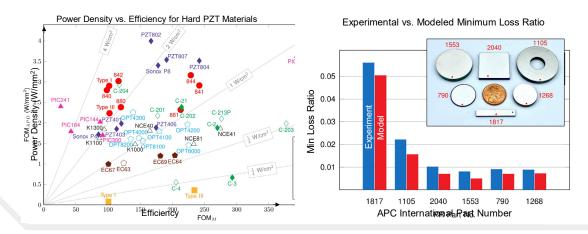

### Materials and Vibration Modes

We evaluate the efficiency and power density capabilities of numerous piezoelectric materials and vibration modes

# Structures and Design Optimization

We develop design guidelines for achieving maximum efficiency and power density in a variety of piezoelectric component structures

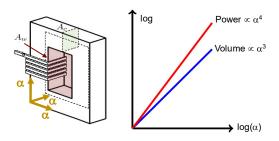

# Geometry optimization Ploss Pout Loss Ratio G FOM Power Density FOM

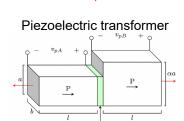

# Fundamental scaling laws show that power density *rises* as volume decreases

# **Experimental Demonstration**

We experimentally demonstrate the drastic miniaturization capabilities of piezoelectrics compared to magnetics

- J. D. Boles et al., "Evaluating Piezoelectric Materials and Vibration Modes for Power Conversion," IEEE TPEL, 2022.

- J. D. Boles et al., "A piezoelectric-resonator-based dc-dc converter demonstrating 1 kW/cm³ resonator power density," IEEE TPEL, 2023.

- J. D. Boles et al., "Piezoelectric-based power conversion: recent progress, opportunities, and challenges,," IEEE CICC, 2022.

Prof. Jessica Boles boles@berkeley.edu

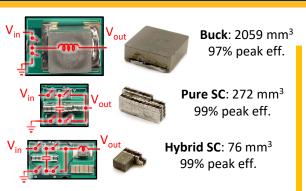

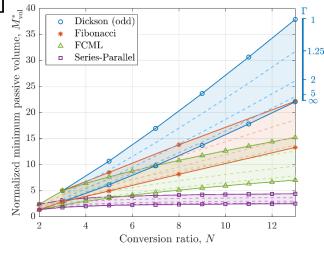

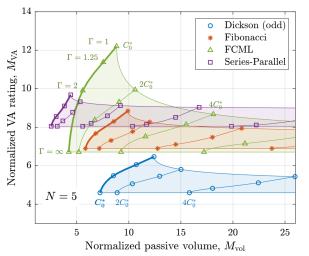

# A General Approach for Design Optimization of High-Performance Hybrid **Switched-Capacitor Converters**

# Berkeley Power and **Energy Center**

# Motivation and Application

Hybrid switched-capacitor converters

- More capacitive energy storage than inductive energy storage for size reduction

- Multiple low-voltage switches in place of a single high-voltage switch for efficiency improvement

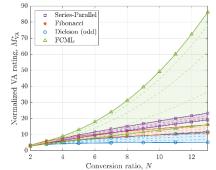

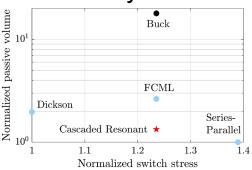

#### **Topology Comparison**

- Analytical method to compare relative size and performance of various topologies

- Include the impacts of capacitor voltage ripple and inductor current ripple on passive component volume and switch stress

Performance comparison at 48V-to-24 V

4 mJ of inductive energy storage

80 mJ of capacitive energy storage (after dc-derating)

Impacts of Switching Frequency and Conversion Ratio on Minimal Passive Volume [1]

- Series-Parallel has smaller passive volume → Higher power density

- Increasing  $\Gamma = \frac{f_{sw}}{f_{res}} \rightarrow$  smaller passive volume → Higher power density

# Passive Component Volume and Switch Stress Trade-Off

# Increasing the switching frequency beyond resonance

Trading ↑ switching loss for ↓ conduction loss

Increasing capacitance beyond minimal volume

Trading ↑ volume for ↓ VA rating (efficiency)

Validation of Analytical Model

Passive component volume for varied capacitance to validate minimal volume method

[1] N. M. Ellis, et. al., "A General Analysis of Resonant Switched Capacitor

Converters Using Peak Energy Storage and Switch Stress Including Ripple," in IEEE Transactions on Power Electronics, Early Access. [2] J. Azurza Anderson, G. Zulauf, J. W. Kolar and G. Deboy, "New Figure-of-Merit Combining Semiconductor and Multi-Level Converter Properties," OJPEL 2020.

Dr. Nathan Ellis, Maggie Blackwell, Rose Abramson, Dr. Nathan Brooks\*, Dr. Sam Coday\* Email: {nathanmilesellis, blackwell, rose abramson} @berkeley.edu

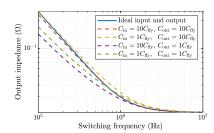

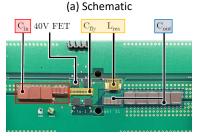

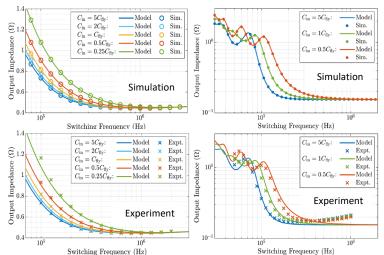

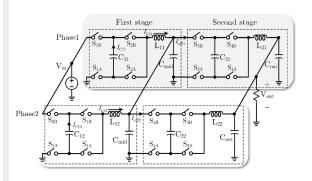

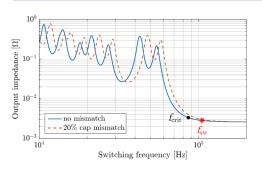

# Modeling and Control of Pure and Resonant Switched-Capacitor Converters with Finite Terminal Capacitances

Berkeley Power and Energy Center

# Background and Motivation

- Insufficient terminal capacitances can greatly affect converter efficiency

- Bulky terminal capacitors become the bottleneck of converter miniaturization

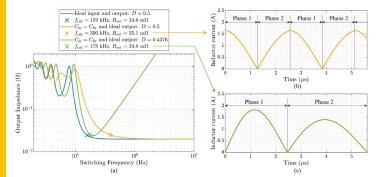

Output impedance of a 2-to-1 pure SC converter with different  $C_{in}$  and  $C_{out}$

Output impedance of a 2-to-1 resonant SC converter with different  $C_{in}$  and  $C_{out}$

Switching Frequency (Hz)

# $V_{\text{in}} \stackrel{L_{\text{par(in)}}}{\longrightarrow} O_{\text{out}} \stackrel{L}{\searrow} R_{\text{load}}$

(b) Hardware prototype 2-to-1 resonant SC (ReSC) converter

# Simulation and Experimental Verification

#### **Key considerations**

- Minimize switching loss

- Accurate parameter acquisition

### High accuracy

waveform of MRCC.

Hardware prototype

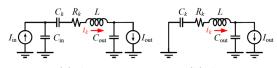

# Modeling Derivation and Effect Analysis

Simplified circuit model and general output impedance model

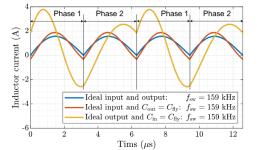

(a) Phase 1 (b) Phase 2 Circuit model of a ReSC converter with  $C_{\rm in}$  and  $C_{\rm out}$

# $I_{\text{in}} \underbrace{ \begin{array}{c} C_k & R_k \\ \hline \end{array}}_{C_{\text{in}}} \underbrace{ \begin{array}{c} C_k & R_k \\ \hline \end{array}}_{I_{\text{out}}} \underbrace{ \begin{array}{c} C_k & R_k \\ \hline$

(a) Phase 1 (b) Phase 2 Circuit model of a pure SC converter with  $C_{\rm in}$  and  $C_{\rm out}$

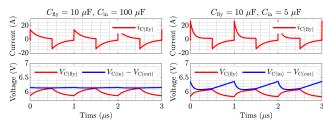

#### Effect of terminal capacitances

Inductor current waveform of a 2-to-1 pure SC converter with different terminal capacitances

Inductor current waveform of a 2-to-1 ReSC converter with different terminal capacitances

# Multi-Resonant Compensation Control (MRCC)

- Challenge: zero current switching (ZCS) is not achievable with 0.5 duty ratio with small  $C_{\rm in}$

- Solution: ensure ZCS operation with the optimal duty ratio and switching frequency

- Result: 5x terminal capacitance reduction without harming efficiency

# (a) Comparison of output impedance. (b) Inductor current waveform of the conventional control. (c) Inductor current

#### References:

- [1] Y. Zhu et al., "Modeling and Analysis of Resonant Switched-Capacitor Converters with Finite Terminal Capacitances," COMPEL 2021.

- [2] Y. Zhu et al., "Multi-Resonant Compensation Control for Terminal Capacitance Reduction in Resonant Switched-Capacitor Converters," COMPEL 2021.

- [3] Y. Zhu et al., "Modeling and Analysis of Switched-Capacitor Converters with Finite Terminal Capacitances," APEC 2021.

Yicheng Zhu, Zichao Ye Email: {yczhu, yezichao}@berkeley.edu

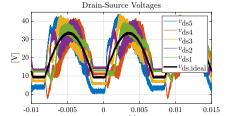

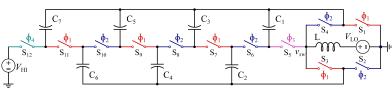

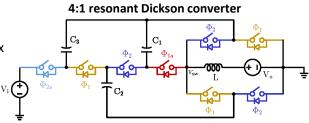

# Analysis of Phase Timings for a Zero-Voltage Switching, Split-Phase Hybrid Dickson Converter

# Motivation and Application

- Dickson-based converters are popular for hybrid switched capacitor (SC) solutions due to the reduced switch stress as compared to other topologies [1]

- Applications: high-conversion ratio systems

- 48 V bus architectures for data centers and automotive powertrains

- Transistor switching losses can be significant share of overall losses, especially with trends towards faster switching frequencies

- Soft-switching techniques, such as zero-current and zero-voltage switching (ZCS and ZVS) can be used to reduce these losses

Switch Stress Metric (VA rating) for various hybrid SC converters over conversion ratios showing the Dickson converter having very low relative switch stress

#### Hardware

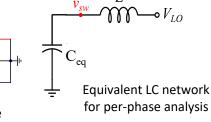

#### 48 V-to-6 V prototype

- Per-phase analysis of an equivalent LC network to determine phase-timings

- Equivalent capacitance Ceq:

- Main phases: A network of the flying capacitors C<sub>1</sub>-C<sub>7</sub>

- ZVS sub-phases: A network of linearized transistor output capacitances [2]

Schematic drawing of the 8-to-1 hybrid Dickson power stage

# Challenges

- Phase-timings become non-trivial to determine

- ZVS timings are also non-trivial

- Non-linear switch output capacitance

- Multiple switches with different blocking voltages

Exemplary phase-timings and waveforms of a resonant Dickson converter achieving ZVS on all switches

#### References:

[1] N. M. Ellis, et. al., "A General Approach to Optimization and Control of Resonant Switched Capacitor Converters Using Peak Energy Storage and Switch Stress Including Ripple Considerations," *IEEE Transactions on Power Electronics, Early Access*.

[2] M. Kasper, R. M. Burkart, G. Deboy, and J. W. Kolar, "ZVS of Power MOSFETs Revisited," IEEE Transactions on Power Electronics, vol. 31, no. 12, pp. 8063–8067, Dec 2016.

## **Experimental Verification**

Measured drain-source voltages showing ZVS for all switches

An efficiency comparison of ZVS to ZCS, as well as calculated timings to fixed timings

Maggie Blackwell Email: blackwell@berkeley.edu

# Autotuning of Resonant Switched-Capacitor Converters for Soft Switching Operation

# Motivation and Application

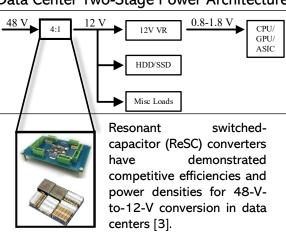

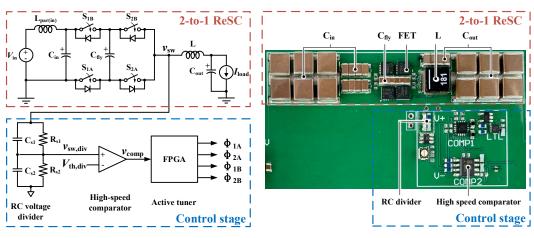

Data Center Two-Stage Power Architecture

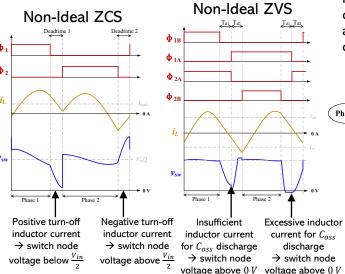

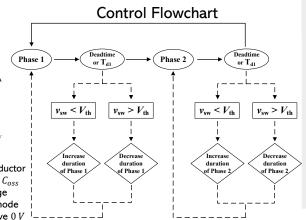

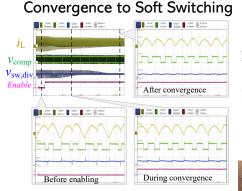

Due to finite terminal filtering capacitances, the efficiency of ReSC converters is often maximized when they are precisely soft switched [4]. However, circuit non idealities render ZCS and ZVS timing challenging to estimate creating the need for active control techniques.

#### **Hardware**

The presented 2-to-1 converter is the foundational ReSC topology. The control technique is verified on a 48-V-to-24-V hardware prototype and can be extended to higher conversion ratio topologies.

## Theory and Control

By sensing the switch node voltage, nonideal soft switching conditions can be detected. Complete ZCS or ZVS can then be achieved by implementing the proposed control scheme.

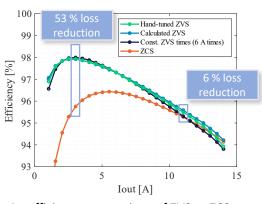

# **Experimental Verification**

- Convergence to complete soft switching can be achieved from a wide range of initial switching frequencies.

- Active ZVS and ZCS control allow for higher peak efficiencies than the conventional openloop techniques.

Output Current [A]

Efficiency

dents: Haifah Sambo, hsambo@berkeley.edu;

Yicheng Zhu yczhu@berkeley.edu;

Post-docs: Ting Ge, gting@berkeley.edu;

Active ZVS

· Active ZCS · Open-loop ZCS

Open-loop ZVS

Poforoncos:

- [1] H. Sambo, Y. Zhu, T. Ge, N. Ellis, and R. Pilawa-Podgurski, "Autotuning of Resonant Switched-Capacitor Converters for Zero Current Switching and Terminal Capacitance Reduction." APEC 2023.

- [2] H. Sambo, Y. Zhu, and R. Pilawa-Podgurski, "Autotuning of Resonant Switched-Capacitor Converters for Zero Voltage Switching," COMPEL 2023.

- [3] T. Ge, Z. Ye, and R. Pilawa-Podgurski, "Geometrical State-Plane Analysis of Resonant

- Switched-Capacitor Converters: Demonstration on the Cascaded Multiresonant Converter," TPEL 2023. [4] Y. Zhu, Z. Ye, T. Ge and R. Pilawa-Podgurski, "Multi-Resonant Compensation Control for Terminal Capacitance Reduction in Resonant Switched-Capacitor Converters." COMPEL 2021.

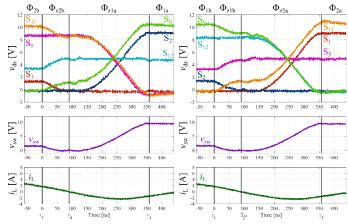

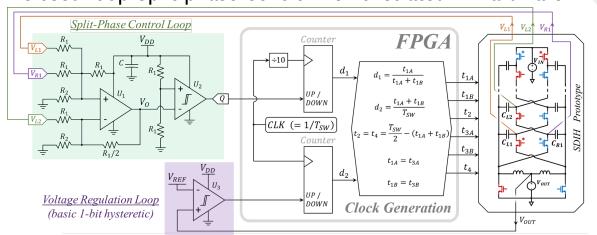

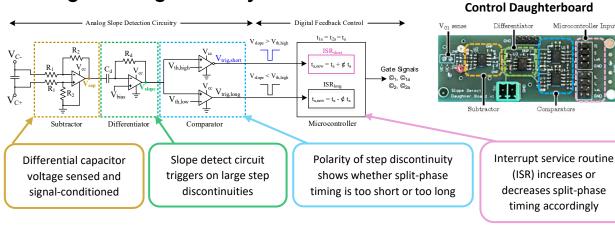

# Closed-Loop Split-Phase Control Applied to a Regulating Point-of-Load (PoL) Dickson-Type Converter

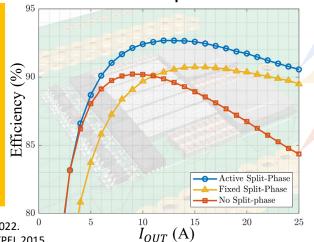

## Motivation and Application

Hybrid Switched Capacitor (HSC) power converter topologies are being adopted in 48V to point-of-load (PoL) applications. Within the HSC converter class, Dickson-type converters [1] achieve the lowest Volt-Amp switch stress, indicative of a smaller semiconductor footprint for equivalent performance. However, some of these topologies require a non-conventional clocking scheme — recently coined as "split-phase switching" [2] — to ensure high efficiency is preserved. Executed in parallel with complimentary work in [3], this work presents a closed-loop split-phase control appropriate for regulating PoL converters [4]; over-coming a key obstacle to the deployment of a new and highly competitive class of hybridized power converter topologies.

### Closed-loop Split-phase Control Demonstrated in Hardware

An added <u>Split-Phase Control Loop</u> detects "hard-charging" events and informs appropriate phase timing adjustments within a conventional FPGA-based clock generator.

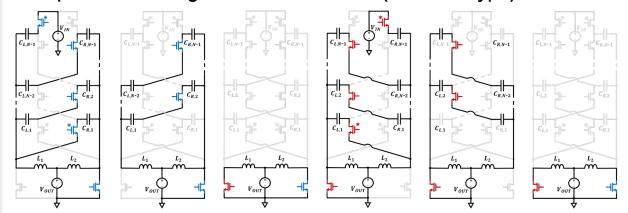

## Example: Phase Progression of the SDIH (Dickson-Type) Converter<sup>[4]</sup>

The duration of all phases are fully constrained as a function of  $V_{IN}$ ,  $V_{OUT}$ ,  $I_{IN}$ ,  $f_{SW}$ , & component values. The practical inclusion of loss and component derating/mismatch necessitates continuous and dynamic phase duration adjustments.

## **Experimental Verification**

Closed-Loop Control

**Theoretical Timings**

Without Split-Phase Control

| <b>Operating Point</b> |         |

|------------------------|---------|

| $V_{IN}$               | 48V     |

| V <sub>OUT</sub>       | 3.3V    |

| $f_{SW}$               | 300 kHz |

[1] N. Ellis, R. Amirtharajah, "Large Signal Analysis on Variations of the Hybridized Dickson Switched-Capacitor Converter," TPEL 2022.

[2] Y. Lei, et. al., "Split-Phase Control: Achieving Complete Soft-Charging Operation of a Dickson Switched-Capacitor Converter," TPEL 2015.

[3] R. Abramson, et. al., "An Active Split-Phase Control Technique for Hybrid Switched-Capacitor Converters Using Capacitor Voltage Discontinuity Detection," COMPEL 2023.

[4] N. Ellis, et. al., "Closed-Loop Split-Phase Control Applied to the Symmetric Dual Inductor Hybrid (SDIH) Converter," COMPEL 2023.

Dr. Nathan Ellis, Haifah Sambo - Email: nathanmilesellis@berkeley.edu

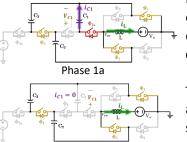

# Active Soft-Charging Control for Hybrid and Resonant Switched-Capacitor Converters

# Motivation and Application

Dickson-derived converters are increasingly used for both **fixed-ratio** and **direct-to-PoL** applications in the datacenter and transportation space. They can achieve **very low switch stress** (i.e. Volt-Amp product), which means that lower-voltage (and therefore less lossy) switches can be used compared to other topologies for a given output power.

#### Split-Phase Control

Certain Dickson topologies require more complex split-phase control schemes [1] in order to achieve full soft-charging of all fly capacitors.

Split-phase control timings can be complex to calculate and vary depending on component tolerance, circuit non-idealities, and operating condition, necessitating active control [2], [3].

The conventional two-phase operation is split into phases {1a, 1b} and {2a,2b}

Capacitor Losses: Hard-Charging vs. Soft-Charging

**Hard-charging:** large charge redistribution loss, spiky currents. **Soft charging:** no charge redistribution loss, smooth / resonant currents.

#### **Phase 1 Split-Phase Operation**

If the {1a,1b} and {2a,2b} transitions occur at the wrong time, hard-charging occurs, resulting in current spikes and discontinuous capacitor voltages.

These voltage steps can be sensed, allowing the controller to auto-tune split-phase times to achieve soft-charging operation.

**Analog Sensing Circuitry**

The analog circuitry is flexible in implementation, and stages can be combined into single package op-amps or off-loaded into internal microcontroller comparator units to increase density.

# **Experimental Verification**

- An 8-to-1 resonant Dickson converter was used for validation.

- The control scheme was able to converge on soft-charging splitphase timing when 1) initialized in a hard charging-condition, and 2) when enabled during load step transients.

# Steady-State Convergence Load Step Transient Load Step Transient Capacitor voltage discontinuity removed Capacitor voltage discontinuity removed Very Very

Smooth capacitor voltages signify soft-charging operation

#### 8:1 Dickson Converter

# 25 V MOSFETS V<sub>C1</sub> sense Inductor C<sub>out</sub>

#### **Operating Conditions**

| Parameter            | Value |

|----------------------|-------|

| $V_{in}$             | 48 V  |

| $V_{out}$            | 6 V   |

| I <sub>out,max</sub> | 10 A  |

Rose Abramson, Sahana Krishnan, Maggie Blackwell Email: {rose\_abramson, sahana\_krishnan, blackwell}@berkeley.edu

#### References:

[1] Y. Lei et al., "Split-Phase Control: Achieving Complete Soft-Charging Operation of a Dickson Switched-Capacitor Converter", IEEE Trans. on Power Electronics, vol. 31, no. 1, pp. 770-782, 2015. [2] R. A. Abramson et al., "An Active Split-Phase Control Technique for Hybrid Switched-Capacitor Converters Using Capacitor Voltage Discontinuity Detection," 2023 IEEE 24th Workshop on Control and Modeling for Power Electronics (COMPEL), Ann Arbor, MI, USA, 2023. [3] N. M. Ellis, H. Sambo and C. N. Robert Pilawa-Podgurski, "Closed-Loop Split-Phase Control Applied to the Symmetric Dual Inductor Hybrid (SDIH) Converter," 2023 IEEE 24th Workshop on Control and Modeling for Power Electronics (COMPEL), Ann Arbor, MI, USA, 2023.

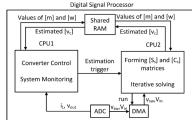

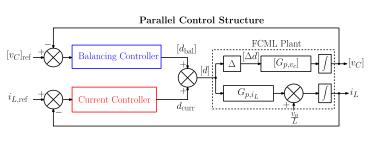

# Closed-Loop Balancing Control and Capacitor Voltage Estimation for the Flying Capacitor Multilevel Converter

# **Balancing Control Motivation**

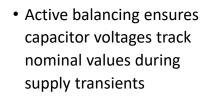

Open-loop balancing of capacitor voltages is unreliable

- Capacitor voltages during large-signal transients exhibit underdamped dynamics

- Peak switch stress may be greater than  $\frac{v_{in}}{N-1}$  and can cause switch overvoltage in high-performance designs using low-voltage switches

#### **Natural Balancing**

## Capacitor Voltage Estimation

- Active balancing requires measurement of capacitor voltages

- Measuring each capacitor voltage with its own differential sensor is expensive

- Can instead measure switched-node voltage with single-ended sensor and calculate capacitor voltages

- Solve system of equations iteratively with reduced computation burden

- Demonstrated on industry-standard Texas Instruments C2000 DSP

First cell's switch states

Capacitor connection matrix

**Estimation**

# **Closed-Loop Control**

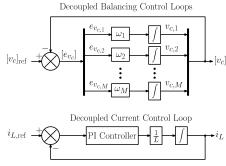

### Equivalent Controllers after Decoupling and Feedback Linearization

- Model average behavior of FCML converter to obtain "plant" for control

- Structure of plant informs controller design: duty ratios can be controlled differentially to steer capacitor voltages

- Balancing controller runs in parallel with controller(s) regulating load voltage

- Closed-loop system is decoupled controllers operate without mutual interaction

# **Experimental Verification**

• Single-sensor estimation of capacitor voltages is reliable and low-cost

# **Active Balancing**

[1] R. K. Iyer, et al., "A High-Bandwidth Parallel Active Balancing Controller for Current-Controlled Flying Capacitor Multilevel Converters," 2023 IEEE Applied Power Electronics Conference and Exposition (APEC).

[2] I. Z. Petric, et al., "A Real-Time Estimator for Capacitor Voltages in the Flying Capacitor Multilevel Converter," 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL).

Rahul Iyer (rkiyer@berkeley.edu), Ivan Petric (ivan.petric@phd.unipd.it)

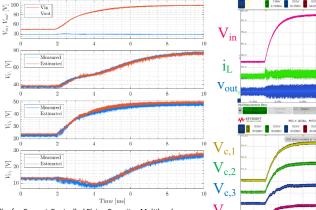

# A Hybrid Switched-Capacitor Solar Microinverter Utilizing a Fixed-ratio Resonant DC-DC Stage and Flying Capacitor Multi-level DC-AC Stage

## Motivation and Application

#### **Hybrid Switched-Capacitor Converters**

- The Cascaded Series-Parallel converter (CaSP)

has been used as a power-dense dc-dc stepdown solution in the 48V application space but

is being adapted use as a boost stage [1].

- The flying capacitor multilevel converter (FCML) can be used to step down the

**Rooftop solar** requires **efficient** and **power dense** solutions to convert power for use in homes and at the grid.

Example inverter: Enphase IQ8

# TI TMDSCNCD28379D L<sub>FCML</sub> Unfolder Connector Connector G-Level FCML FCML

#### **CaSP System Specifications**

• 35-40V input

Hardware

• 350-400V, 500W output

#### **FCML System Specifications**

- 350-400V input, 500W+

- Sensing for control included on this board.

- 2nd revision coming soon

# dc dc dc dc ac 60 Hz ac Full microinverter concept.

## System Architecture

- Three sub-intervals of one switching cycle, each with a unique resonant LC tank impedance [2].

- Achieves ZCS, partial ZVS.

- Can be used as standalone startup circuitry.

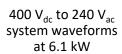

- 400V to 240Vac. Voltage at output of inductor is rectified sine wave that is unfolded by H-bridge.

- HV buffer allows for reduction of capacitance due to smaller current ripple

# **Experimental Validation**

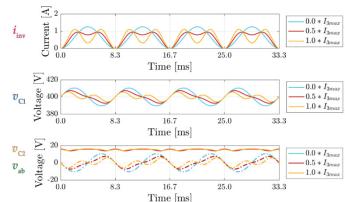

Peak efficiency with 255 Vac output at light load: 93.5%

#### System waveforms with 240 V<sub>ac</sub> output

- System able to produce 240 Vac output at light load

- CaSP achieves ZCS during full system operation at 240 Vac output

#### References:

[1] R. A. Abramson, Z. Ye, T. Ge and R. C. N. Pilawa-Podgurski, "A High Performance 48-to-6 V Multi-Resonant Cascaded Series-Parallel (CaSP) Switched-Capacitor Converter," 202 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 2021

[2] K. Fernandez and R. C. N. Pilawa-Podgurski, "A 1-to-10 Fixed-Ratio Step-up Multi-Resonant Cascaded Series-Parallel (CaSP) Switched-Capacitor Converter with Zero-Curren Switching," 2023 11th International Conference on Power Electronics and ECCE Asia (ICPE 2023 - ECCE Asia), 2023

Kelly Fernandez, Francesca Giardine Email: kefernandez@berkeley.edu, fgiardine@berkeley.edu

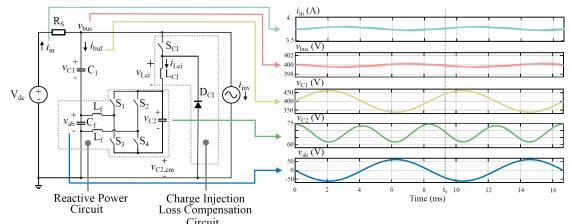

# A Charge Injection Loss Compensation Method for a Series-Stacked Buffer to Reduce Current and Voltage Ripple in Single-Phase Systems

Berkeley Power and Energy Center

# Motivation and Application

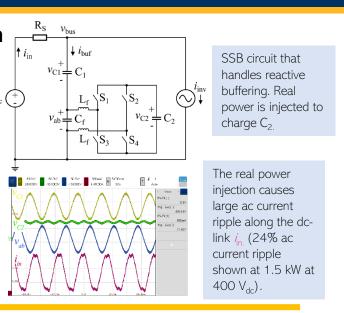

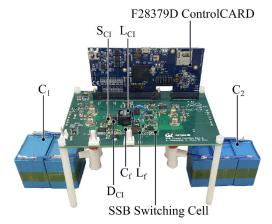

The Series-stacked buffer (SSB) is an active buffer topology that achieves high energy utilization and greatly decreases the power  $V_{dc}$  conversion system volume without comprising efficiency [2]. However, there can be a large amount of residual ac current ripple on the dc bus due to SSB's control methodology that injects real power through the reactive buffer branch. This control is required to charge the  $C_2$  capacitor in the SSB that acts as a dc source for a full-bridge converter. Specifically, this ripple gets is worse in applications with low source impedance, such as battery systems.

#### Hardware

| Component       | Part No.                       | Parameters       |

|-----------------|--------------------------------|------------------|

| $S_1 - S_4$     | EPC2033                        | 150 V, 6 mΩ      |

| S <sub>CI</sub> | GaN Systems GS66506T           | 600 V, 2 A       |

| D <sub>CI</sub> | ON Semiconductor<br>MURS160T3G | 650 V, 67 mΩ     |

| L <sub>CI</sub> | Coilcraft MSS1210-104          | 100 μΗ           |

| $C_1$           | TDK B32524Q1686K000            | 100 V, 68 μF x 3 |

| C <sub>2</sub>  | TDK B32776G4406K000            | 450 V, 40 μF x 2 |

|                 |                                |                  |

Proof of concept hardware. GaN devices are used for all switches. The volume of this design can be further reduced by using the optimization methodology shown in [3].

# Proposed "Charge Injection" Method

The Charge Injection method has a separate branch that handles real power delivery while the rest of the SSB handles the reactive power buffering. As a result, the dc-link current ripple is greatly reduced.

## **Experimental Verification**

The peak-to-peak ac current ripple is reduced:

- By maximum of **5.3x**

- And average of 4.3x

- 3x at peak load

Charge Injection method achieves an average **efficiency of 99.4%** across all loads.

#### References:

[1] K. Fernandez, N. Brooks, T. Ge, Z. Liao, R. C. N. Pilawa-Podgurski, "A Charge Injection Loss Compensation Method for a Series-Stacked Buffer to Reduce Current and Voltage Ripple in Single-Phase Systems" in 2022 Applied Power Electronics Conference (APEC), 2022.

[2] Z. Liao, et al. "A High Power Density Power Factor Correction Converter with a Multilevel Boost Front-End and a Series-Stacked Energy Decoupling Buffer," 2018 IEEE Energy Conversion Congress and Exposition (ECCE), 2018, pp. 7229-7235, [3] Z. Liao, et al. "Multi-objective optimization of series-stacked energy decoupling buffers in single-phase converters," in 2018 IEEE19th Workshop on Control and Modeling for Power Electronics (COMPEL), July 2018, pp. 1–7.

Student Name: Kelly Fernandez, kefernandez@berkeley.edu

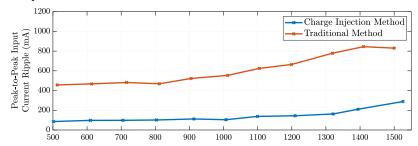

# Utilizing Harmonic Injection to Reduce Energy Storage in a Single-Phase Active Energy Buffer

#### **Motivation**

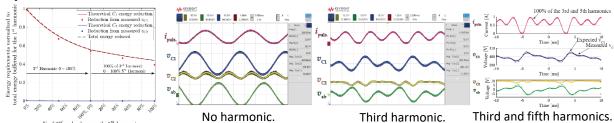

- Single-phase power converters rated for high power applications require reactive buffering on the dc bus to maintain a constant and clean dc power input or output. Often this is a bulky electrolytic capacitor.

- [1] found that buffer storage requirements for a passive buffer could be reduced 56% for the addition of allowable 3<sup>rd</sup> and 5<sup>th</sup> harmonics

- We apply this harmonic injection method for energy storage reduction in the capacitors of the series-stacked buffer (SSB), which is a power-dense alternative to the conventional capacitor solution.

Energy storage in buffer during a twice-line frequency cycle.

$$W_{store} = \int_0^{\frac{T_{2l}}{2}} P_{buff}(t) \, \mathrm{d}t$$

$$W_{store} = \frac{1}{2}CV_{max}^2 - \frac{1}{2}CV_{min}^2$$

## Circuit Topology and Hardware

The SSB is an active buffer that combines a primary energy buffer capacitor with an H-bridge. This permits a larger voltage ripple across the main energy storage capacitor maximizing the amount of energy buffered, and subsequently the energy utilization ratio [2].

# Challenges and Control

- Determining the expected voltage ripple on each of the capacitors is nontrivial.

- Figure out how to control an active buffer when additional harmonics are added to the system.

## **Experimental Verification**

55% reduction in required energy storage split between two capacitors. In an example case,  $C_1$  can be reduced from  $60\mu F$  to  $34\mu F$ , and  $C_2$  from  $27\mu F$

to  $20\mu F$  for same dc-bus voltage ripple [3].

#### Poforoncos:

[1] A. J. Hanson, A. F. Martin, and D. J. Perreault, "Energy and Size Reduction of Grid-Interfaced Energy Buffers Through Line Waveform Control," IEEE Transactions on Power Electronics, Nov. 2019

[2] N. C. Brooks, S. Qin, and R. C. N. Pilawa-Podgurski, "Design of an active power pulsation buffer using an equivalent series-resonant impedance model," in 2017 IEEE 18th Workshop on Control and Modeling for Power Electronics, Jul. 2017

[3] F. Giardine, N. C. Brooks, K. Fernandez and R. C. N. Pilawa-Podgurski, "Utilizing Harmonic Injection to Reduce Energy Storage and Required Capacitance in an Active Series-Stacked Energy Buffer for Single-Phase Systems," 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics, 2022

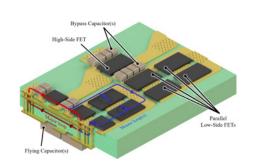

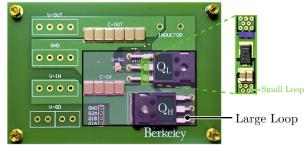

# Advanced Switching Cell Design Techniques

Berkeley Power and **Energy Center**

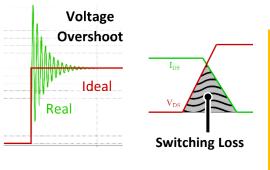

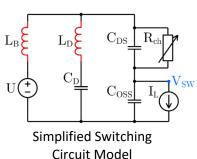

# Motivation and Application

Power converters operate by switching between different circuit states. Ideally, the switching transitions would be instantaneous and lossless. In reality, parasitic effects cause switching losses, voltage overshoot, and electromagnetic interference. Advanced design techniques are presented here, which mitigate these effects and enable unprecedented performance.

load current and output capacitance of the device:

$C_D^* = 10 * \max\{C_{OSS}, 2L_B I_{ML}^2 / U_{ML}^2\}$

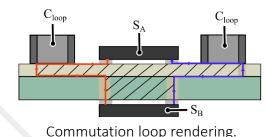

# Interleaved Commutation Loop Layout [2]

Commutation loop inductance is critical to switching performance. Advanced layout techniques can be utilized to reduce this inductance.

Interleaved hybrid decoupling capacitor loops with electrically thin vertical bulk capacitor loop

Table 1: Commutation Loop Comparison Switching Cell Electrically Hybrid & Hybrid Proposed Design Simulated 1.15 nHInductance Measured

Isometric Vie

- Proposed design achieves nearly 3x better performance than best approach without decoupling capacitors

- 20% better than state of the art

# **Optimal Decoupling** Capacitor Sizing [1]

Experimental Data Determined optimal decoupling capacitor size given

-Large Overshoot

Effect of  $C_D$  on Overshoot

Decoupling Capacitance Ratio  $(C_D/C_D^*)$

# Decoupling Device [3]

For many applications, transistors with large through-hole packages are used, due to their high power handling capability. In this work, a small surface-mount galliumnitride transistor is added to improve switching performance.

Buck converter hardware prototype

50% reduction in losses

Inductance Board Area

- [1] L. Horowitz and R. C. N. Pilawa-Podgurski, "On Decoupling Capacitor Size in GaN-Based Power Converters," 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL), Tel Aviv, Israel, 2022, pp. 1-5, doi: 10.1109/COMPEL53829.2022.9830000

- [2] L. Horowitz and R. C. N. Pilawa-Podgurski, "Modular Switching Cell Design for High-Performance Flying Capacitor Multilevel Converter," 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 2022, pp. 342-347, doi:

- [3] L. Horowitz, N. M. Ellis and R. C. N. Pilawa-Podgurski, "Decoupling Device for Small Commutation Loop and Improved Switching Performance with Large Power Transistors," 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 2023, pp. 2620-2624, doi: 10.1109/APEC43580.2023.10131426.

Logan Horowitz | Email: logan h horowitz@berkeley.edu

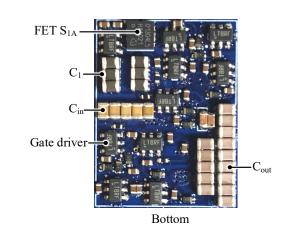

# High-Performance 48-to-12 V Cascaded Multi-Resonant Switched-Capacitor Converter for Datacenters

Berkeley Power and **Energy Center**

# Motivation and Applications

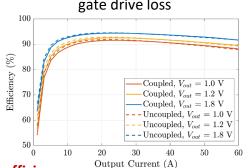

48 V data center power delivery architecture

- The intermediate bus converter in 48 V data center application requires high efficiency and high power density

- Regulation and isolation are not required

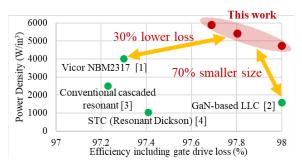

#### Hardware Demonstration

- Dimensions:  $17.3 \times 23 \times 6.6$  mm power density: 6000 W/in<sup>3</sup> at 12 V output

- 80 A continuous output and 130 A 2 ms transient output

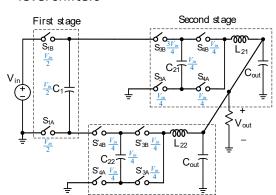

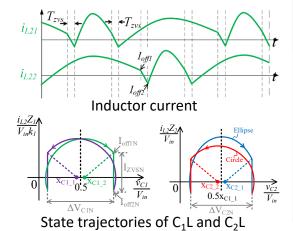

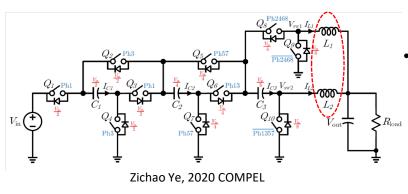

# Proposed Topology

- Cascaded Multi-Resonant converter

- 1st stage uses only two switches to the save space of active components, and gate drive level shifters

State-plane method is used to calculate multi-resonant inductor current

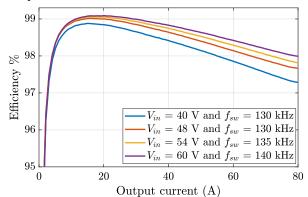

## **Experimental Results**

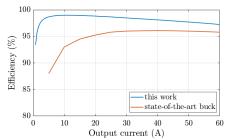

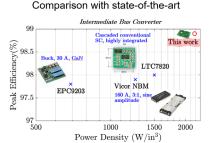

Comparison with State-of-the-Art 48-to-12 V Solutions

Measured efficiencies including gate drive loss

Reference: T. Ge, Z. Ye and R. C. N. Pilawa-Podgurski, "A 48-to-12 V Cascaded Multi-Resonant Switched Capacitor Converter with 4700 W/in3 Power Density and 98.9% Efficiency," 2021 IEEE ECCE.

Email: gting@berkeley.edu Ting Ge

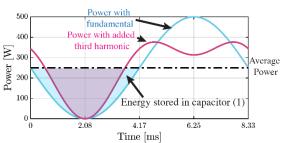

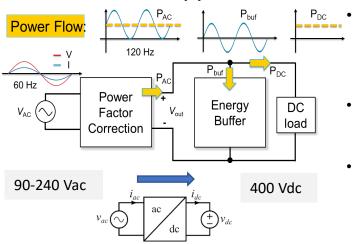

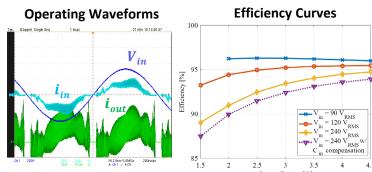

# High Performance Single-phase Ac-dc Conversion with Advanced Topology and Control

# Motivation and Application

- 90-240 Vac to 400 Vdc is a critical conversion stage for applications such as data center power delivery, electric vehicle charging, etc.

- Ac-dc power factor correction

- Reduce boost inductor size

- Twice-line frequency power ripple buffering

Reduce buffer capacitor size

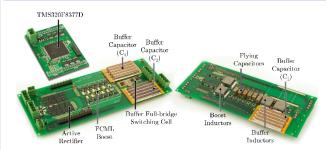

# Hardware Implementation

90-240 Vac to 400 Vdc, 1.5 kW PFC converter [1]

- Single DSP TMS320F28377D for the proposed system control

- GaN System and EPC GaN FETs used in FCML and SSB for high efficiency

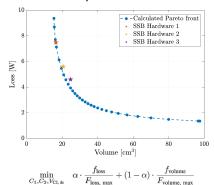

#### Multi-objective optimization for SSB<sup>[2]</sup>

Loss-volume Pareto front of SSB generated with numerical optimization method

# Challenges and Solutions

### Topology

- The boost inductor size is reduced flying capacitor multilevel (FCML) topology

- An active buffer topology seriesstacked buffer (SSB) is implemented to reduce the buffer capacitor for twice-line frequency power ripple buffering

#### Control

#### **PFC+SSB Coupled Control:**

- PFC Multi-loop control: high-bandwidth "inner" current & low-bandwidth "outer" voltage loop

- PFC Partial feedforward cancels the input voltage disturbances to input current caused by smaller boost inductor in FCML

- **Buffer control** obtains phase and amplitude information from PFC

# **Experimental Verification**

| Total box-volume power density: | 230 W/in <sup>3</sup> |

|---------------------------------|-----------------------|

| Peak efficiency:                | 98.9%                 |

| 1.5 kW efficiency:              | 98.1%                 |

| THD:                            | < 5%                  |

| Power factor:                   | > 0.994               |

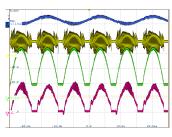

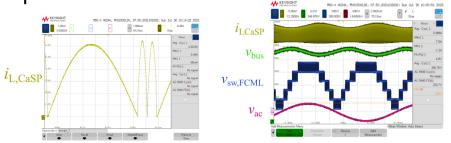

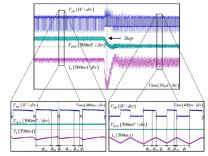

Experimental waveforms demonstrating power factor correction, multi-level switching, and SSB @ 1.5 kW, 240 Vac to 400 Vdc

#### References:

[1] Z. Liao. N. C. Brooks, and R. C. N. Pilawa-Podgurski, "A high power density power factor correction converter with a multilevel boost front-end and a series-stacked energy decoupling buffer," in 2018 IEEE Energy Conversion Congress and Exposition (ECCE), 2018

[2] Z. Liao, et al. "Multi-objective optimization of series-stacked energy decoupling buffers in single-phase converters," in 2018 IEEE19th Workshop on Control and Modeling for Power Electronics (COMPEL), July 2018, pp. 1-7.

Student: Zitao Liao. Email: zliao5@berkeley.edu

# High Efficiency High Power Density Hybrid/Resonant Switched-Capacitor Converter

# Theoretical Analysis

#### Switch VA rating

$\left(\begin{array}{cc} \sum_{i=1}^{n} V_{ds}I_{ds} \right)$

Total passives volume

$$\left(\frac{\frac{1}{2}\sum CV^2}{\rho_{E,C}} + \frac{\frac{1}{2}\sum LI^2}{\rho_{E,L}}\right)$$

- Systematically analyze and calculate switch and passive utilization

- Compare and select the most suitable topology depending on application and power level

- Develop control technique to achieve soft-charging and softswitching

#### Cascaded Resonant Converter

#### Two-phase interleaved design

Overcome the intermediate decoupling challenge of doubler topology

#### Zero voltage switching technique

Operate the tank in the inductive region to achieve ZVS, while improving tolerance of component variations

# **Practical Challenges and Solutions**

#### Floating gate drive

- Improved bootstrap and charge pump techniques to replace isolated dc/dc power supplies

- Achieving higher efficiency, lower cost and smaller footprint

- Working on system level circuit integration to further reduce size and cost

### Capacitor voltage balancing

- 0.56 -- D-0.125 -- D-0.150 -- D-0

- Experimentally verified that source impedance and input capacitance can affect balancing drastically

- Even-level FCML converter has better natural balancing

- Gate drive voltage and signal mismatch can cause imbalance

# **Experimental Verification**

#### References:

[1] Z. Ye, Y. Lei, W. Liu, P. S. Shenoy and R. C. N. Pilawa-Podgurski, "Design and implementation of a low-cost and compact floating gate drive power circuit for GaN-based flying capacitor multi-level converters," *APEC 2017* [2] Z. Ye, Y. Lei, Z. Liao and R. C. N. Pilawa-Podgurski, "Investigation of capacitor voltage balancing in practical implementations of flying capacitor multilevel converters", *COMPEL 2017* [3] Z. Ye, Y. Lei and R. C. N. Pilawa-Podgurski, "A resonant switched capacitor based 4-to-1 bus converter achieving

2180 W/in3 power density and 98.9% peak efficiency," *APEC 2018*

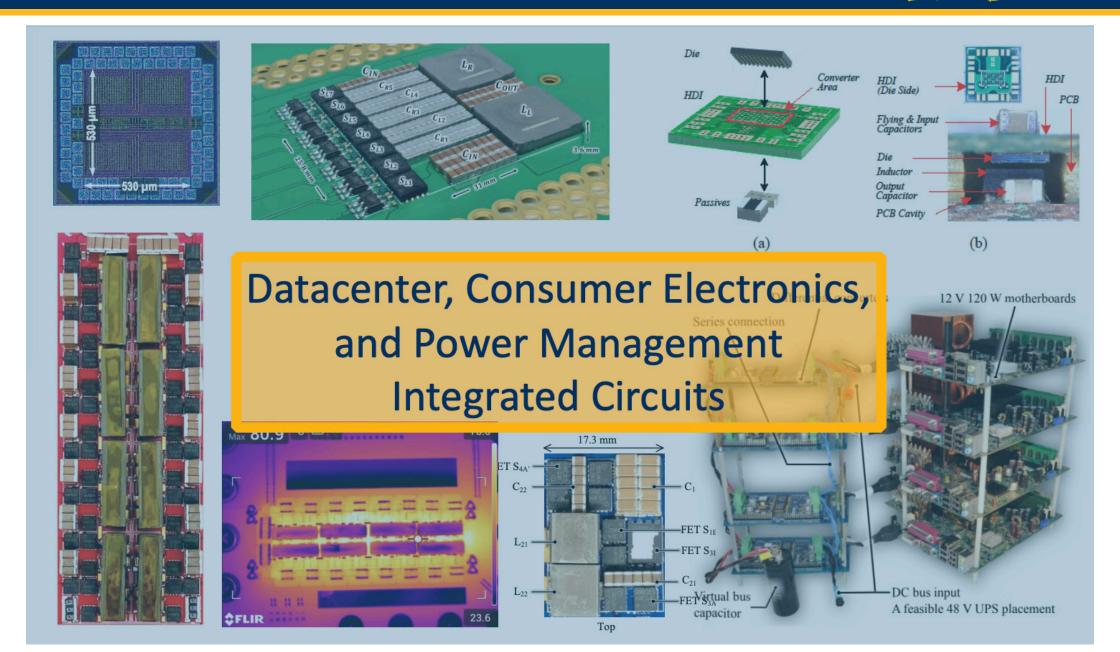

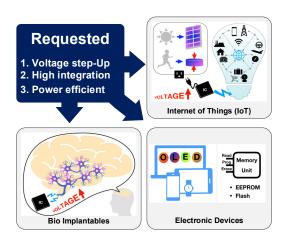

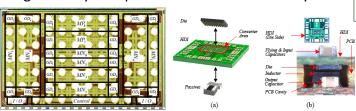

# Motivation and Applications

High voltages are demanded to

- Generate efficacious stimulations for bio-implantable devices

- Interface between low-voltage energy harvesters and batteries for wireless sensor network (WSN)

- Program memories for high operational speeds

- Drive LED strings efficiently

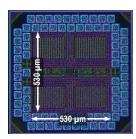

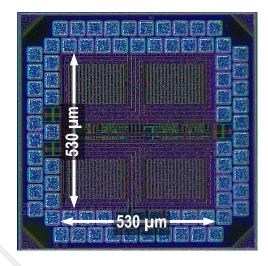

## Chip Implementation

- TSMC 65nm CMOS process

- 2.5V devices for 5.0V operation

# Challenges and Solutions

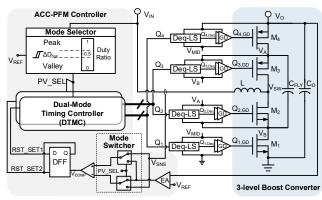

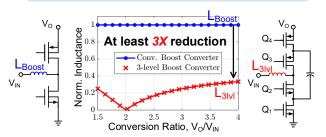

#### Topology: 3-level Boost Converter

Hybrid SC converters merge the advantages of the conventional switched capacitor (SC) and switched inductor converters (e.g. Boost converter)

- Achieve high power density

- Mitigate charge sharing loss in SC converter

- Retain the ability to employ low voltage

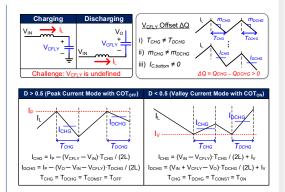

#### Control: ACC-PFM

ACC-PFM is an integrated controller solution for both V<sub>OUT</sub> regulation and capacitor balancing

#### Measurement Results

| Peak Efficiency                | 96.8%                      |

|--------------------------------|----------------------------|

| Input Voltage                  | 0.3 – 3V                   |

| Output Voltage                 | 2.4 – 5V                   |

| Peak Output Current            | 83 mA                      |

| Peak Switch<br>Current Density | 300<br>mA/ mm <sup>2</sup> |

| Switching Freq.                | 0.5M – 45MHz               |

Excellent performance for wide-range voltage and load variation required in stepup applications, compared to prior arts.

#### References:

Wen-Chuen Liu, Pei Han Ng, Robert C.N. Pilawa-Podgurski, "An 83mA 96.8% Peak Efficiency 3-Level Boost Converter with Full-Range Auto-Capacitor-Calibrating Pulse Frequency Modulation", IEEE Custom Integrated Circuits Conf. (CICC), 2019.

Student: Wen-Chuen Liu Email: joseph.wcliu@berkeley.edu

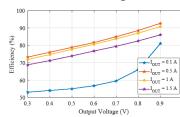

# A 94.2%-peak-efficiency 1.53A direct-battery-hook-up hybrid Dickson switched-capacitor DC-DC converter with wide continuous conversion ratio in 65nm CMOS

# Berkeley Power and Energy Center

# Motivation and Application

Increased power density of advanced CMOS nodes in embedded

applications requires the power converters to have:

- Higher efficiency to extend the battery life

- · Low loss to ease the thermal management

- · Higher power density to match the technology

- Maintain performance at large conversion ratios

Typical Battery voltage 3.2 V to 4.2 V

Typical Load voltage 300m V to 1 V

Typical Load current several mA to several A

# NFC module (and hardware for Apple Pay) WiFi module Audio codec M8 motion coprocessor Codec M8 motion coprocessor Radio receive-only chip for carrier aggregation Touchscreen Primary Power Secondary Power RF

controller Management

**Increasing Gap**

Control

#### Hardware

4 mm2

- Implemented in CMOS 65nm bulk process

- Flip-Chip packaging for low parasitic

- Voltage borrowing gate drive to eliminate bootstrap capacitors and increase power density

- Active capacitor balancing and output regulation

- External flying capacitors and inductor

- High density interposer for uModule assembly

$C_{1} C_{2} C_{3} C_{4} C_{4$

System Architecture

uModule Assembly

# Challenges and Solutions

$\label{thm:converters} \mbox{Utilized hybrid switched-capacitor (SC) converters.}$

Switched-Capacitor stage:

- Higher efficiency at large conversion ratios

- Lower rated devices for advance CMOS integration

- Poor regulation

#### Magnetic Buck stage:

- Achieve tighter regulation

- Lower voltage swing for smaller magnetics

Need higher utilization of passive and active devices:

- Dickson SC has good switch utilization and poor capacitor utilization

- Soft-charging through split-phase control increases capacitor utilization, enhances efficiency and lower switching frequency

- Smaller passives for faster transient response and tighter control

# Split-Phase

4:1 Hybrid Dickson

# **Experimental Verification**

Maintained efficiency and power density:

- Across large conversion ratios

- Across large load current range

# Output regulation and flying capacitor active balancing

**Reference:** W. Liu, P. Assem, Y. Lei, P. K. Hanumolu and R. Pilawa-Podgurski, "10.3 A 94.2%-peak-efficiency 1.53A direct-battery-hook-up hybrid Dickson switched-capacitor DC-DC converter with wide continuous conversion ratio in 65nm CMOS," *ISSCC 2017*.

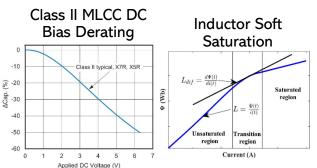

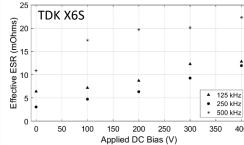

# Characterization of Multi-layer Ceramic Capacitors under More Realistic Operating Conditions

Berkeley Power and Energy Center

# Motivation and Applications

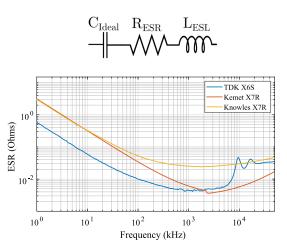

- Multi-layer ceramic capacitors (MLCCs) are a key enabling technology for high density power converters.

- Real losses in MLCCs can be reduced to equivalent series resistance (ESR)

- Data sheets do not provide loss information for realistic operating conditions.

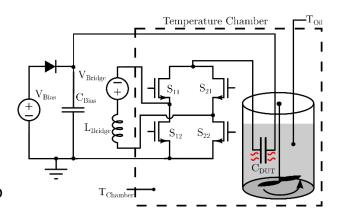

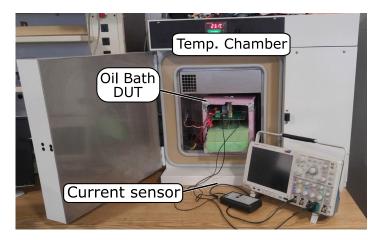

## Hardware Implementation

- ESR is dependent on frequency, DC bias, AC amplitude, temperature and harmonic content.

- A circuit was designed to be able to adjust frequency, current amplitude and DC bias of a high harmonic content waveform in order to test the effect on ESR.

# Challenges and Solutions

$$P_{diss} = \frac{1}{T_{final}} \left( k_{oil} \, \Delta temp + \int_{0}^{T_{final}} \frac{temp_{oil} - temp_{amb}}{R} \, dt \right) [1]$$

- Measuring loss with electrical characterization is in accurate under desired operating conditions.

- A calorimetric method was implemented in order to accurately observe change in ESR.

# Experimental Results

| Capacitor<br>Manufacturer | Capacitor De-<br>rating<br>(at 400 V) | ESR increase<br>(at 400 V, 125 kHz) |

|---------------------------|---------------------------------------|-------------------------------------|

| TDK                       | 80%                                   | 200%                                |

| Knowles                   | 82%                                   | 243%                                |

| Kemet                     | 72%                                   | 142%                                |

• With increased DC bias, the ESR linearly increases, this has been shown with several dielectric types as well as manufacturers.

#### References:

[1] G. S. Dimitrakakis, E. C. Tatakis, and A. C. Nanakos, "A simple calorimetric setup for the accurate measurement of losses in power electronic converters," *EPE 2011*.

[2] S. Coday, C. B. Barth and R. C. N. Pilawa-Podgurski,

"Characterization and Modeling of Ceramic Capacitor Losses under Large Signal Operating Conditions," COMPEL 2018.

Student: Samantha Coday Email: scoday@berkeley.edu

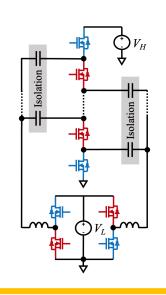

# Hybrid Switched-Capacitor DC-DC Converters with Isolation

# Motivation and Applications

- Hybrid switched-capacitor converters offer high power density but have been restricted to non-isolated applications

- Traditional isolation methods require bulky and heavy transformers

- Capacitive isolation presents a power-dense alternative to magnetic isolation

- Flying capacitors with high voltage rating act as isolation capacitors

# Theory of Operation

- Capacitively isolated hybrid switched-capacitor converter based on [1], [2]

- Complete soft-charging of capacitors eliminates loss from transient inrush currents

- 50% duty cycle and two-phase operation

- Switch voltage stress independent of load

# Challenges and Solutions

- ZVS theoretically possible, but not successful at higher input voltages

- Ongoing issue; we'll spend more time investigating timing

- Light-load oscillations that damage converter at higher voltages

- Current solution: avoid light load

# [1] Y. Li, L. Gu, A. Hariya, Y. Ishizuka, J. Rivas-Davila, and S. Sanders, "A wide input range isolated stacked resonant switched-capacitor dc-dc converter for high conversion ratios," in 2018 IEEE 19th Workshop on Control and Modeling for Power Electronics (COMPEL), 2018, pp. 1–7.

[2] N. M. Ellis and R. Amirtharajah, "A resonant dual extended lc-tank dickson converter with 502021 IEEE Applied Power Electronics Conference and Exposition (APEC), 2021, pp. 1282–1287.

# **Experimental Results**

• 94.1% peak efficiency, 2,010 W/in<sup>3</sup> power density

Output Power [W]

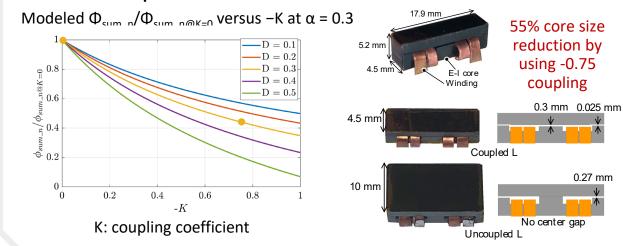

# Core Size Scaling Law of Two-Phase Coupled Inductors – Demonstration in a 48-to-1.8 V MLB (Multi-Level-Binary)-PoL Converter

# Motivation and Applications

Multi-Level Binary (MLB) hybrid switchedcapacitor converter for 48 V to PoL conversion

- In Point-of-Load (PoL) applications, inductors usually occupy >50% total volume

- A general core-size model is desired to evaluate the duty-ratio advantage of hybrid converters and guide magnetic design

## Hardware Implementation

# Proposed Method and Result

2-phase coupled inductors: schematic, core structure, current waveforms, and flux densities

Total flux is proportional to core size and calculated by:

$$\begin{bmatrix} \Phi_{1\_max} \\ \Phi_{2p} \end{bmatrix} = \begin{bmatrix} L_s & KL_s \\ KL_s & L_s \end{bmatrix} \begin{bmatrix} I_{1p} \\ I_{2p} \end{bmatrix} / N$$

$$\Phi_{sum\_N} = \frac{\Phi_{sum} f_{sw} N}{V_{out}}$$

$$= \frac{4}{\alpha (1 - K)} - \left(\frac{4}{\alpha} + 2\right) D + \frac{3}{2}$$

# **Experimental Results**

| Converter speci             | fications    |           |

|-----------------------------|--------------|-----------|

| $V_{in}$                    | 48 V         |           |

| Max. $V_{out}$              | 1.8 V        |           |

| Max. D                      | 0.3          |           |

| Max. $I_{out}$              | 65 A         | Co        |

| $f_{sw}$                    | 250 kHz      | (Th       |

| α                           | 0.3          | Un        |

| Design 1: coupled inductors |              | · cm      |

| K                           | -0.75        | (Th       |

| $L_s$                       | 800 nH       | [1<br>con |

| esign 2: uncouple           | ed inductors | dis       |

| L                           | 517 nH       |           |

|                             |              |           |

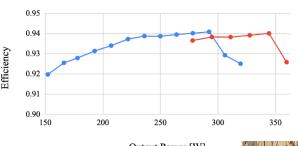

# Converter performance summary

|                                       | Efficiency at 48 V input and 1.8 V output | Power density<br>& Dimensions             |

|---------------------------------------|-------------------------------------------|-------------------------------------------|

| Coupled L<br>(This work)              | Peak: 94.4%<br>Full load: 91.5%           | 474 W/in³<br>26×18.4×7.8 mm               |

| Uncoupled<br>L<br>(This work)         | Peak: 94.5%<br>Full load: 91.6%           | 391 W/in <sup>3</sup><br>31.5×18.4×7.8 mm |

| [1] using<br>commercial<br>discrete L | Peak: 94.0%<br>Full load: 91.3%           | 329 W/in <sup>3</sup><br>29×18.4×10.1 mm  |

# Measured efficiency including gate drive loss

The converter with coupled L achieves **0.4% higher peak efficiency** and **44% higher power density** compared to the discrete counterpart.

α: ripple factor, defined by the peak-to-peak inductor current over the maximum dc current

**Reference:** T. Ge, R. Abramson, Z. Ye, and R. C. N. Pilawa-Podgurski, "Core Size Scaling Law of Two-Phase Coupled Inductors – Demonstration in a 48-to-1.8 V Hybrid Switched-Capacitor MLB-PoL Converter," 2022 APEC.

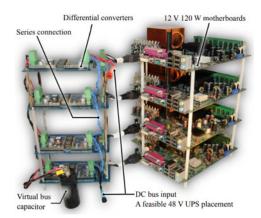

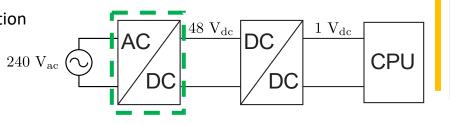

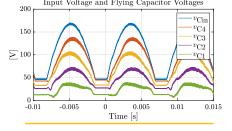

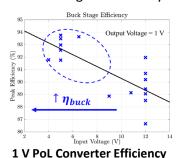

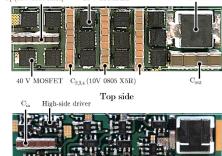

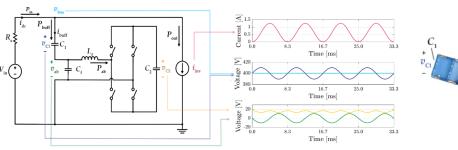

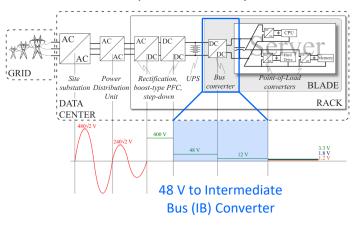

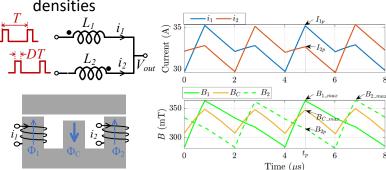

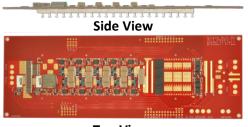

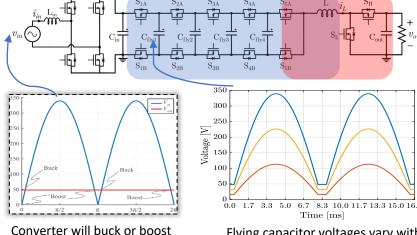

# Motivation and Application

Traditional data center power factor correction (PFC) units boost voltage before rectification and step-down

<u>Proposed</u>: A one-stage single-phase ac-dc converter (240 Vac to 48 Vdc) with PFC

| Metrics         | Existing     | Proposed |

|-----------------|--------------|----------|

| Peak Efficiency | 94 %         | 97.8 %   |

| Power Density   | 0.33<br>kW/L | 7.5 kW/L |

## Hardware Prototype

#### **Top View**

#### **Operating Parameters**

| Number of Levels       | 6      |

|------------------------|--------|

| Switching<br>Frequency | 40 kHz |

| Output Current         | 4.5 A  |

#### **Current Compensation to Improve Power Factor**

Displacement current from  $C_{in}$  and  $C_{fly}$  leads to a phase shift in the input current, degrading the power factor. Our improved control algorithm compensates for this current to improve power factor [1].

# Challenges and Solutions

depending on point in AC

input line cycle

Flying capacitor voltages vary with ac line cycle → unique challenges with capacitor balancing

Buck:  $S_H$  ON,  $S_L$  OFF;  $S_{\{1,2,3,4,5\}A}$  and  $S_{\{1,2,3,4,5\}B}$  modulate

$\begin{aligned} & \text{Boost: } S_{\{1,2,3,4,5\}A} \\ & \text{ON,} S_{\{1,2,3,4,5\}B} \text{ OFF; } S_L \\ & \text{and } S_H \text{modulate} \end{aligned}$

Preliminary prototype tests buck functionality, so that the converter is off when  $|V_{in}| < V_{out}$ .

The converter relies on a stiff 48 V at the output (i.e. the UPS)

# **Experimental Verification**

# Performance Specifications 94.8% at 240 Vac, 250 W Volume (Box) 2.45 in³ 163 W/in³ (w/o heatsink) 79 W/in³ (w/ heatsink)

#### References:

[1] E. Candan, A. Stillwell, N. Brooks, R. Abramson, J. Strydom, R. C. N. Pilawa-Podgurski, "A 6-level Flying Capacitor Multi-level Converter for Single Phase Buck-type Power Factor Correction," in *Proceedings of 2019 IEEE Applied Power Electronics Conference and Exposition (APEC)*, March 2019.

Rose Abramson, Nathan Brooks Email: {rose\_abamson, nathanbrooks}@berkeley.edu

# Advanced Techniques for Driving Floating Switches in the Flying Capacitor Multi-level converter

# Berkeley Power and **Energy Center**

# Motivation and Application Floating switches need floating power supplies • Typically use isolated power supply for each switch • Large volume (due to isolation transformer) and high cost 6 W Isolated auxiliary power supply for SiC-MOSFET gate driver "Cascaded bootstrap" proposed for reduced volume and cost

# Charge-Pump Technique